系统化的良率分析方法

发布时间:2017/11/21 21:15:39 访问次数:589

limited yieId

半导体△产制造中时常用yield作为指标来进行分析。在很多时候,由于测试顺序等原/xl,yield对于失效机制的反映存在一定的偏差,所以需要引limi1ed yield这个概念。 TC4053BF

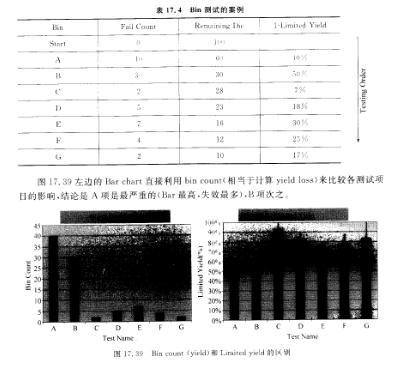

表17.1是一个hn测试的案例。共有A~G七个测试项日,测试顺序从A到G,有100个样品用于这项测试。采用⒏F(stop on hl)测试,即某样品任一项日测试失效,停止余下项日测试,转到下一样品。⒏)F测试是在半导体生产制造中常用的wafer yield测试方法,和与之对应的C()F(continue on hl)测试比较而言,它能节约测试时间,lm测试时问和测试成本成正比。

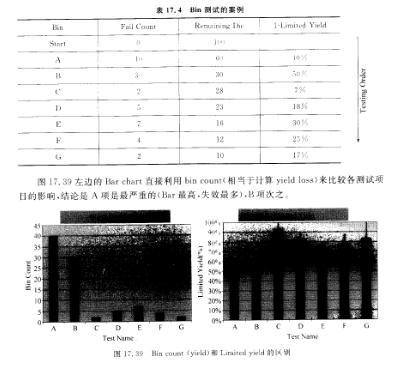

图17.39左边的Bar chart直接利用bin∞unt(相当于计算yield loss)来比较各测试项日的影响,结论是A项是最严重的(Bar最高,失效最多),B项次之。

limited yieId

半导体△产制造中时常用yield作为指标来进行分析。在很多时候,由于测试顺序等原/xl,yield对于失效机制的反映存在一定的偏差,所以需要引limi1ed yield这个概念。 TC4053BF

表17.1是一个hn测试的案例。共有A~G七个测试项日,测试顺序从A到G,有100个样品用于这项测试。采用⒏F(stop on hl)测试,即某样品任一项日测试失效,停止余下项日测试,转到下一样品。⒏)F测试是在半导体生产制造中常用的wafer yield测试方法,和与之对应的C()F(continue on hl)测试比较而言,它能节约测试时间,lm测试时问和测试成本成正比。

图17.39左边的Bar chart直接利用bin∞unt(相当于计算yield loss)来比较各测试项日的影响,结论是A项是最严重的(Bar最高,失效最多),B项次之。

热门点击

热门点击

- PⅤD Ti

- 光刻分辨率的表示

- 线宽均匀性

- 良率学习(yield Iearning)速度

- CMOs与鳍式MOsFET(FinFET)

- FA的案例

- 非破坏性分析

- 把机器人制造单元分为以下三种类型

- 非零初始状态和死锁

- 椭偏仪

推荐技术资料

推荐技术资料

- DS2202型示波器试用

- 说起数字示波器,普源算是国内的老牌子了,FQP8N60... [详细]

公网安备44030402000607

公网安备44030402000607