不同电容值的匹配设计

发布时间:2016/6/28 23:29:22 访问次数:543

图8.19(a)所示的2只晶体管的版图方向不同,匹配性能很差;图8.19(b)所示的2只晶体管的版图方向一致,但是两晶体管源漏极的周围环境不同,ADS1118这会引起源漏极的掺杂浓度、多晶硅刻蚀速率的不匹配,因此会增加两晶体管之间的不匹配;图8.19(c)通过增加“冗余”单元保证了每个晶体管周围的环境相同,因此减小了晶体管的不匹配。

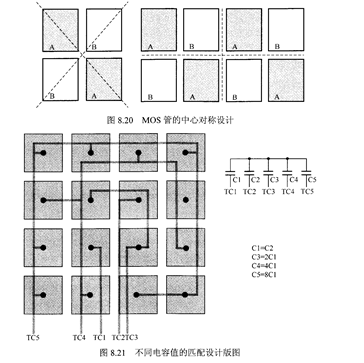

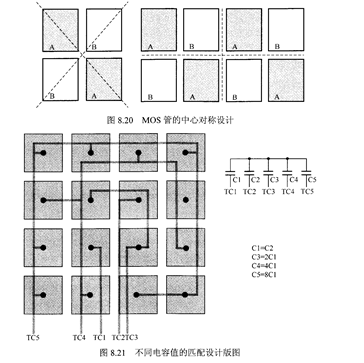

图8.⒛所示是采用重心重合的MOS管设计。图8.21给出了5个电容值之比为1∶⒈⒉⒋8的匹配电容在采用了单元元器件复制技术、公用重心设计技术后的版图,综合采用这些技术,可以提高多个电容之间的匹配性能。

采用版图匹配设计技术后可以提高元器件的匹配性能,但是会增加芯片面积,布线也会比较困难,连线的寄生效应会限制匹配精度。

图8.19(a)所示的2只晶体管的版图方向不同,匹配性能很差;图8.19(b)所示的2只晶体管的版图方向一致,但是两晶体管源漏极的周围环境不同,ADS1118这会引起源漏极的掺杂浓度、多晶硅刻蚀速率的不匹配,因此会增加两晶体管之间的不匹配;图8.19(c)通过增加“冗余”单元保证了每个晶体管周围的环境相同,因此减小了晶体管的不匹配。

图8.⒛所示是采用重心重合的MOS管设计。图8.21给出了5个电容值之比为1∶⒈⒉⒋8的匹配电容在采用了单元元器件复制技术、公用重心设计技术后的版图,综合采用这些技术,可以提高多个电容之间的匹配性能。

采用版图匹配设计技术后可以提高元器件的匹配性能,但是会增加芯片面积,布线也会比较困难,连线的寄生效应会限制匹配精度。

公网安备44030402000607

公网安备44030402000607