LTC6903CMS8TR 数据选择器的好处是无的转动

发布时间:2020/2/10 19:20:14 访问次数:1678

LTC6903CMS8TR逻辑函数产生器,根据8选1数据选择器输出与输人的关系式(4.4.7)有式中mi是地址选择输入端s2、s1、sO构成的最小项。数据输入作为控制信号,当DJ=1时,其对应的最小项祝g在表达式中出现,当Di=0时,对应的最小项就不出现。利用这一点将函数变换成最小项表达式,函数的变量接入地址选择输入端,就可以实现组合逻辑函数。

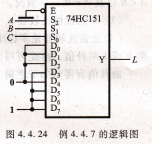

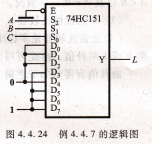

例4,4,7 试用8选1数据选择器74HC151产生逻辑函数L=ABC+ABC+AB。

解:把所给的函数式变换成最小项表达式

L=ABC+A BC+ABC+AB C

将上式写成如下形式

L=m3D3+5D5+m6D6+m7D7

显然D3、D5、D6、D7都应该等于1,而式中没有出现的最小项mO、m1、m2、m4对应的数据,输入端D0、D1、D2、D4都应该等于0,并将使能端接低电平。由此可画出该逻辑函数产生器的逻辑图,如图4.4.24所示。

通过上面例题可以看出,与使用各种逻辑门,设计组合逻辑电需对函数化简路相比,数据选择器的好处是无的转动.

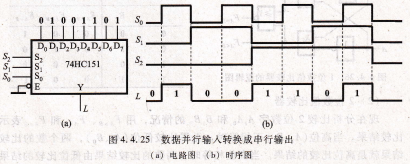

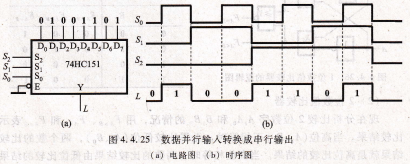

图4.4.24 例4.4.7的逻辑图,成的并/串行转换的电路图。选择照图中所给波形从图4.4.25 数据并行输入转换成串行输出(a)电路图 (b)时序图.

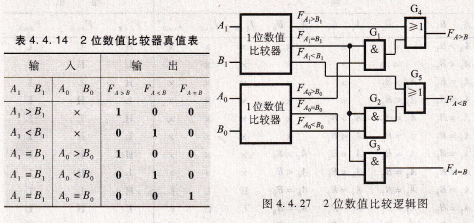

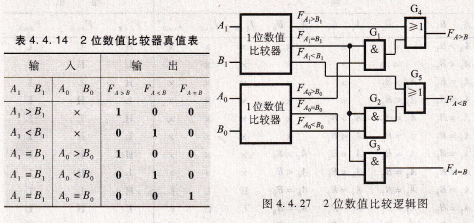

若干典型的绍合逻辑集成电路决定。利用1位数值的比较结果,可以列出简化的真值表,如表4,4,14所示。

表4.4.14 2位数值比较器

F1>u=A1B1+(A1B1+A1B1)Bl

=F.1>1+FA1=1・FA>Bo

F1=Fa1+F.1=k・FA0<20

F4=y=F.1=1・F=0=t。

根据上式画出逻辑图,如图4.4.27所示。电路利用了1位数值比较器的输出作为中间结果。它所依据的原理是,如果2位数我A。和B1B。的高位不相等,则高位比较结果就是两数比较结果,与低位无关。这时,高位输出F.1=t1=0,使与门G1、G2、G3均封锁,而或门都打开,低位比较结果不能影响或门,高位比较结果则从或门直接输出。如果高位相等,即F=u=1,使与门G1、G2、G3均打开,同时由于F.1>1=0和FAl<k=0作用,或门也打开,低位的比较结果直接送达输出端,即低位的比较结果决定两数谁大、谁小或者相等。

用以上的方法可以构成更多位数值比较器。

集成数值比较器常用的中规模集成数值比较器有CMOs和TTL的产品。74x85是4位数值比较器,74x682是8位数值比较器。这里主要介绍74HC85。

集成数值比较器74HC85的功能,集成数值比较器74HC85是4位数值比较器,其功能如表4,4.15所示,输人端包括A3~A0与B3~B。,输出端为Fu>x、F<j、FA=£,以及扩展输人端为r1>i、f<r和rd=g。扩展输人端与其他数值比较器的输出连接,以便组成位数更多的数值比较器。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

LTC6903CMS8TR逻辑函数产生器,根据8选1数据选择器输出与输人的关系式(4.4.7)有式中mi是地址选择输入端s2、s1、sO构成的最小项。数据输入作为控制信号,当DJ=1时,其对应的最小项祝g在表达式中出现,当Di=0时,对应的最小项就不出现。利用这一点将函数变换成最小项表达式,函数的变量接入地址选择输入端,就可以实现组合逻辑函数。

例4,4,7 试用8选1数据选择器74HC151产生逻辑函数L=ABC+ABC+AB。

解:把所给的函数式变换成最小项表达式

L=ABC+A BC+ABC+AB C

将上式写成如下形式

L=m3D3+5D5+m6D6+m7D7

显然D3、D5、D6、D7都应该等于1,而式中没有出现的最小项mO、m1、m2、m4对应的数据,输入端D0、D1、D2、D4都应该等于0,并将使能端接低电平。由此可画出该逻辑函数产生器的逻辑图,如图4.4.24所示。

通过上面例题可以看出,与使用各种逻辑门,设计组合逻辑电需对函数化简路相比,数据选择器的好处是无的转动.

图4.4.24 例4.4.7的逻辑图,成的并/串行转换的电路图。选择照图中所给波形从图4.4.25 数据并行输入转换成串行输出(a)电路图 (b)时序图.

若干典型的绍合逻辑集成电路决定。利用1位数值的比较结果,可以列出简化的真值表,如表4,4,14所示。

表4.4.14 2位数值比较器

F1>u=A1B1+(A1B1+A1B1)Bl

=F.1>1+FA1=1・FA>Bo

F1=Fa1+F.1=k・FA0<20

F4=y=F.1=1・F=0=t。

根据上式画出逻辑图,如图4.4.27所示。电路利用了1位数值比较器的输出作为中间结果。它所依据的原理是,如果2位数我A。和B1B。的高位不相等,则高位比较结果就是两数比较结果,与低位无关。这时,高位输出F.1=t1=0,使与门G1、G2、G3均封锁,而或门都打开,低位比较结果不能影响或门,高位比较结果则从或门直接输出。如果高位相等,即F=u=1,使与门G1、G2、G3均打开,同时由于F.1>1=0和FAl<k=0作用,或门也打开,低位的比较结果直接送达输出端,即低位的比较结果决定两数谁大、谁小或者相等。

用以上的方法可以构成更多位数值比较器。

集成数值比较器常用的中规模集成数值比较器有CMOs和TTL的产品。74x85是4位数值比较器,74x682是8位数值比较器。这里主要介绍74HC85。

集成数值比较器74HC85的功能,集成数值比较器74HC85是4位数值比较器,其功能如表4,4.15所示,输人端包括A3~A0与B3~B。,输出端为Fu>x、F<j、FA=£,以及扩展输人端为r1>i、f<r和rd=g。扩展输人端与其他数值比较器的输出连接,以便组成位数更多的数值比较器。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公网安备44030402000607

公网安备44030402000607