LT1116CS8TR��������·�ĸ���˺���λ�˲��õĴ�������

����ʱ��:2020/1/29 12:58:45 ���ʴ���:1095

LT1116CS8TR�˲�������Ч�����Ƹ���,��������ϸ��ŵ�����.

��ϵͳ����ϲ���(�ر��ǵ��ߡ�����)�IJ���Ӧʹ��ϵ��ݾ���С,ʹ���߾�����,����뾡����,����������ƽ������,�Լ�С��������ϡ�

�Ը���Դ�ͱ������߽��е�����,���ܸ��ŵĴ���������������ʹ������ϵ�ѹ�ܵ����ơ�

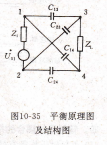

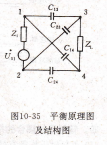

�������Դ���Ŷ���Ļ����·���������,��ɲɵ�ƽ���ʩ�����������Ը���,ͼ10-35��ʾ����ƽ���ʩ��ԭ��ͼ���ṹͼ,ƽ������Ϊ

C13:C23==Cn:C24

���������ýṹ�Դ�ʩ��ʵ��,���ɲ���ƽ���������ʵ��,��Ҫ�Ľṹ�Դ�ʩ��:�ٲ������ĵ���;�ڵ�����ʺ�(1ͬ2, 3ͬ4)��

�������ϸ��ŵ�����,����ϵͳ�ĵ�����,��Ҫ�ǵ��ߺ͵��¼����ϡ�

ʹ����뾡����,���߾�����,����ƽ�����߲��跨��С������·��Χ�ɵ����ʹ���о�����С,�������Ƶ������ϡ�

�Ը��Ŷ�������Դ���д�����,�����ƴų����,������ԭ����10.3.1��ʾ��

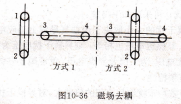

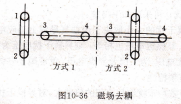

�����ŵĵ����ڸ��ų��еķ��÷�λӦʹ���Ը��Ŵų��и�Ĵ���������,��������ϵĸ����ź�Ҳ��С��ͼ10-36��ʾ���ǵ��������ֿ��ܵ����÷�λ,����������������ֱ,��˴���ų�ȥ������С��

��һ�������Ļ�·���Ƴɼ��Խ��������ɾֲ���ϻ�(�ʺ���),��ͼ10-37,ʹ֮�ص��߳��ȷ���ķ��Ž���ľֲ�����źű˴��������ͼ��QΪ����Դ��·,�������·Ϊ�ʺ���,ʹ�伫�Խ��������ھֲ���ϻ�����Χ�������Ĵų�Hn��Im�����;ͼ��EΪ�����Ż�·,���·��·���ýʺ���,ʹ֮���ھֲ���ϻ��ϵĸ�Ӧ��ѹ����ƽ��ԭ��ͼ���ṹͼ,�෴�������;��˲��ýʺ�������Ч�����Ƶ���Ĵ���ϡ���λ�������ʺϴ���Խ����ʺ�����ҲԽ��,�Ե���,�ʺϴ���ԼΪ30��ÿ�ס�

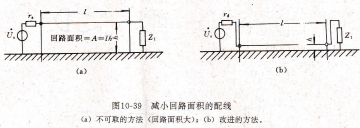

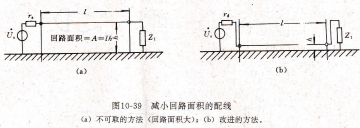

�罫���������ʺϵĵ���ͬʱ���ڹ����ĵ��²���,ÿ���ʺ����ڵ�λ���ȵĽʺϴλ�·���,��С��·���������,(a)����ȡ�ķ���(��·�����);(b)�Ľ��ķ�����

������·�ȳ��Ķ���,��������ӵ��ŵ�·��������ʱ,��ʹrC1�����7ohֵ����,yolֵ��������ǰ����֪,��ض�ʹ��·������������,���������������������������,�ӿ����ŵĽǶȿ���,Ҫ���·��������ز�Ҫ�������涨���ȳ���,����Ӧ�����ܵ����г�ֵ�����,��ͼ10-39��ʾ��

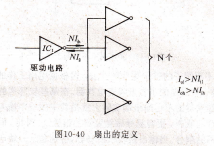

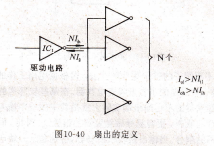

�������ۼ��ɵ�·��ʹ�õ����롢����˵Ĵ������������뿹���ŵĹ�ϵ�����ɵ�·��ʹ��ʱ�������������롢����˻���ƶ˿��Ų��á�����,һ��������˵�����������ШD��������˲���;һ������������ֻ��Q����˶�Q�˿��Ų���,ֻ�ø���˶�������λ�˵ȡ�������Щ���Ų��õĶ���һ��Ҫ���ƴ���,��������������ͨ���ֲ����ݶ�������Щ����,�Ե�·��ɸ��š�һ���TTL��CMOS��·�IJ��ö��Ӵ�����ͼ10-40��ʾ,ͼ��(a)��ʾ�����ñȵ�Դ��ѹ�Ե�һЩ�Ķ�����Դ,�����еIJ��ö����������,ʹ���ö��ӱ���Ϊ�ߵ�ƽ������һ�����İ취,������ȱ����Ҫ��һ����ѹ�ȵ�Դ��ѹ�Ե͵Ķ�����Դ,����Ȼ�����á�ֻ��TTL��74LSϵ�е�·,����������˵����������ѹ�ϸ�,���õĶ��ӿ���ֱ�ӽӵ�Դ��ѹ5V,��������·��Ҫ���ڱ�5V�͵ĵ�Դ�ϡ�ͼ(b)�dz��õķ���,���õĶ��ӿ���1~10 k���ĵ�����ycc��Դ��ӡ�Ϊ��ʡ����Ҳ�ɽ�������õ�����˹���һ�����衣��TTL��·,һ��1 k������һ�������20������õ�����ˡ�ͼ(c)�İ취Ҳ��ʹ��,���ǽ����õĶ�����ʹ�õĶ��Ӳ��ӡ���Ҫע��,�����ö˽϶�ʱ����һ������ʹ�ö˲���,�⽫����ǰ����·���ȳ���������˵Ҫע���ɴ�������������Ľ��͡�ͼ(d)�ķ����ǽ����õ�����˽��ڵ�·����δʹ�õ�������ϡ����ַ���һ��Ҫ�ӵ���ȷ,�Ա�֤�����һֱΪ�ߵ�ƽ��ͼ(e)�Ǵ�������·�ĸ���˺���λ�˲��õĴ���������

������Ψ�жȿƼ�����˾http://wydkj.51dzw.com/

LT1116CS8TR�˲�������Ч�����Ƹ���,��������ϸ��ŵ�����.

��ϵͳ����ϲ���(�ر��ǵ��ߡ�����)�IJ���Ӧʹ��ϵ��ݾ���С,ʹ���߾�����,����뾡����,����������ƽ������,�Լ�С��������ϡ�

�Ը���Դ�ͱ������߽��е�����,���ܸ��ŵĴ���������������ʹ������ϵ�ѹ�ܵ����ơ�

�������Դ���Ŷ���Ļ����·���������,��ɲɵ�ƽ���ʩ�����������Ը���,ͼ10-35��ʾ����ƽ���ʩ��ԭ��ͼ���ṹͼ,ƽ������Ϊ

C13:C23==Cn:C24

���������ýṹ�Դ�ʩ��ʵ��,���ɲ���ƽ���������ʵ��,��Ҫ�Ľṹ�Դ�ʩ��:�ٲ������ĵ���;�ڵ�����ʺ�(1ͬ2, 3ͬ4)��

�������ϸ��ŵ�����,����ϵͳ�ĵ�����,��Ҫ�ǵ��ߺ͵��¼����ϡ�

ʹ����뾡����,���߾�����,����ƽ�����߲��跨��С������·��Χ�ɵ����ʹ���о�����С,�������Ƶ������ϡ�

�Ը��Ŷ�������Դ���д�����,�����ƴų����,������ԭ����10.3.1��ʾ��

�����ŵĵ����ڸ��ų��еķ��÷�λӦʹ���Ը��Ŵų��и�Ĵ���������,��������ϵĸ����ź�Ҳ��С��ͼ10-36��ʾ���ǵ��������ֿ��ܵ����÷�λ,����������������ֱ,��˴���ų�ȥ������С��

��һ�������Ļ�·���Ƴɼ��Խ��������ɾֲ���ϻ�(�ʺ���),��ͼ10-37,ʹ֮�ص��߳��ȷ���ķ��Ž���ľֲ�����źű˴��������ͼ��QΪ����Դ��·,�������·Ϊ�ʺ���,ʹ�伫�Խ��������ھֲ���ϻ�����Χ�������Ĵų�Hn��Im�����;ͼ��EΪ�����Ż�·,���·��·���ýʺ���,ʹ֮���ھֲ���ϻ��ϵĸ�Ӧ��ѹ����ƽ��ԭ��ͼ���ṹͼ,�෴�������;��˲��ýʺ�������Ч�����Ƶ���Ĵ���ϡ���λ�������ʺϴ���Խ����ʺ�����ҲԽ��,�Ե���,�ʺϴ���ԼΪ30��ÿ�ס�

�罫���������ʺϵĵ���ͬʱ���ڹ����ĵ��²���,ÿ���ʺ����ڵ�λ���ȵĽʺϴλ�·���,��С��·���������,(a)����ȡ�ķ���(��·�����);(b)�Ľ��ķ�����

������·�ȳ��Ķ���,��������ӵ��ŵ�·��������ʱ,��ʹrC1�����7ohֵ����,yolֵ��������ǰ����֪,��ض�ʹ��·������������,���������������������������,�ӿ����ŵĽǶȿ���,Ҫ���·��������ز�Ҫ�������涨���ȳ���,����Ӧ�����ܵ����г�ֵ�����,��ͼ10-39��ʾ��

�������ۼ��ɵ�·��ʹ�õ����롢����˵Ĵ������������뿹���ŵĹ�ϵ�����ɵ�·��ʹ��ʱ�������������롢����˻���ƶ˿��Ų��á�����,һ��������˵�����������ШD��������˲���;һ������������ֻ��Q����˶�Q�˿��Ų���,ֻ�ø���˶�������λ�˵ȡ�������Щ���Ų��õĶ���һ��Ҫ���ƴ���,��������������ͨ���ֲ����ݶ�������Щ����,�Ե�·��ɸ��š�һ���TTL��CMOS��·�IJ��ö��Ӵ�����ͼ10-40��ʾ,ͼ��(a)��ʾ�����ñȵ�Դ��ѹ�Ե�һЩ�Ķ�����Դ,�����еIJ��ö����������,ʹ���ö��ӱ���Ϊ�ߵ�ƽ������һ�����İ취,������ȱ����Ҫ��һ����ѹ�ȵ�Դ��ѹ�Ե͵Ķ�����Դ,����Ȼ�����á�ֻ��TTL��74LSϵ�е�·,����������˵����������ѹ�ϸ�,���õĶ��ӿ���ֱ�ӽӵ�Դ��ѹ5V,��������·��Ҫ���ڱ�5V�͵ĵ�Դ�ϡ�ͼ(b)�dz��õķ���,���õĶ��ӿ���1~10 k���ĵ�����ycc��Դ��ӡ�Ϊ��ʡ����Ҳ�ɽ�������õ�����˹���һ�����衣��TTL��·,һ��1 k������һ�������20������õ�����ˡ�ͼ(c)�İ취Ҳ��ʹ��,���ǽ����õĶ�����ʹ�õĶ��Ӳ��ӡ���Ҫע��,�����ö˽϶�ʱ����һ������ʹ�ö˲���,�⽫����ǰ����·���ȳ���������˵Ҫע���ɴ�������������Ľ��͡�ͼ(d)�ķ����ǽ����õ�����˽��ڵ�·����δʹ�õ�������ϡ����ַ���һ��Ҫ�ӵ���ȷ,�Ա�֤�����һֱΪ�ߵ�ƽ��ͼ(e)�Ǵ�������·�ĸ���˺���λ�˲��õĴ���������

������Ψ�жȿƼ�����˾http://wydkj.51dzw.com/

�������

�������

- DS31256B ����ϵͳά��ע������

- p2098 �жϵ�ѹ�ͱ���©������

- LTC2050HS5TRPBF ��ѹ������

- T405-700B-TR��ϵͳ����ɼ�����ԭ

- FS10VS-12A B-2682�Ͳ���ѭ��

- XC5210-6PC84C �μ���ϵͳ�Ͳ���

- PX0840/A/5M00��������ʹ�ù�����

- HM658512LFP-12 �������ȵ���Ч

- S1R72003B00A100�����ѹ����

- M29KW016E-90N1ˮƽ������İ�װ

�Ƽ���������

�Ƽ���������

- ���ƾ����1875����

- ƽʱ��Ҳ������һЩ����DIY��̳�������кܶ���ϲ��LM... [��ϸ]

- ��һ������8ϵ���콢оƬӦ���о�

- ��Դ��ͨ�˲���(RC4558DN)Ӧ�����

- WTC6216����ʽ�������Ӧ

- ��Ƕ��ʽ�洢��ASIC��SoC����ص�����

- 16V��8A Silent Switcher

- ����ƥ���˲�оƬ

- ��ý��Э������SM501��Ƕ��ʽϵͳ�е�Ӧ��

- ����IEEE802.11b��EPA�¶ȱ�����

- QUICCEngine�������ƶ�IP�������

- SoC���������IJ�ҵ����

- MPC8xxϵ�д�������Ƕ��ʽϵͳ��Դ���

- dsPIC�����ڽ�����Ƶ�����е�Ӧ���о�

��������44030402000607

��������44030402000607