ma4p505-1072-30 淘汰的主要原因是受当时工艺所限

发布时间:2020/1/16 17:53:57 访问次数:1020

ma4p505-1072-30全局布线资源主要用于分配时钟信号和其他贯穿整个器件的高扇出信号。

这些布线资源分为主、次两级。主全局布线资源与提供高扇出时钟信号的专用输入引脚构成4个专用全局网络,每一个全局时钟网络可以驱动所有的CLB、IOB和RAM块的时钟引脚。有4个全局缓冲器分别驱动这4个主全局网络。

12根穿越时钟引脚的芯片顶部限制,所以比主布线资源使用更灵活。

信号的传输延时是限制器件工作速度的根本原因。在FPGA的设计过程中,由软件进行优化,确定电路布局的位置和线路选择,以减小传输延迟时间,提高工作速度。

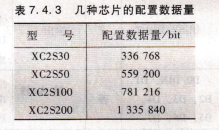

FPGA编程简介,配置(编程)数据,由7.4.2节介绍看出,FPGA中的CLB、都是由它们相应的存储单元中的数据确IOB的功能和布线资源的连接,表7,4.3 几种芯片的配置数据量数据。将配置数据写人FPGA芯片后,该芯片便具有了所设计的功能。FPGA的规模不同,其所需配置数据量也不同,表7.4.3所示为Spartan-Ⅱ系列芯片的几个例子。

配置数据由FPGA开发软件①自动生成。开发系统将设计输人转换成网表文件,并自动对逻辑电路进行划分、布局和布线,然后按PROM格式生成配置数据流文件。可以用通用或专用编程器将配置数据写入PROM中。根据FPGA芯片型号所需配置数据量的多少选择相应容量的PROM。

配置数据的装入,由于SRAM在掉电后其内部的数据会丢失,所以基于SRAM的FPGA必须配置一个PROM芯片,用以存放FPGA的配置数据。每次上电后,FPGA可以自动将PROM中的配置数据装载到FPGA中,或通过控制FPGA相应的编程引脚,将配置数据装载到FPGA中。装载完成后,FPGA按照配置好的逻辑功能开始工作。

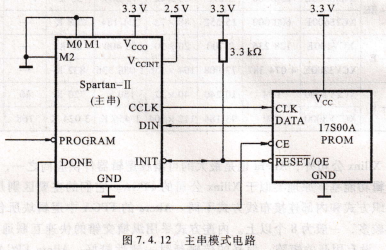

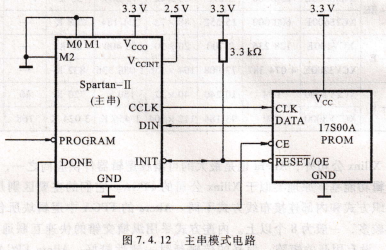

例如Xlllnx公司的1SE软件或其他第三方软件,明场可编程闸阵型号,配置数据量bit,当选择串行模式时,编程数据从PROM中以串行方式装人FPGA中,此时必须用有串行功能的PROM。主串装人模式电路如图7.4.12所示。当选择并行模式时,除了时钟信号外,还需提供其他读写控制信号。

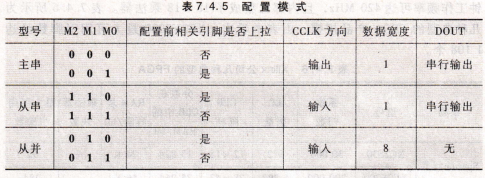

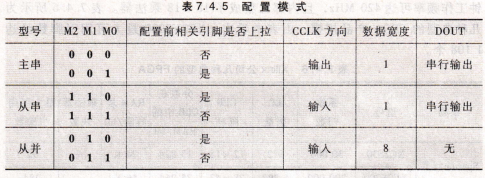

表7,4.5配置模式,主串模式电,FPGA不仅能够直接从PROM中,读取配置数或单片机控制装入配置数据。

近年来,随着半导体工艺的进一步提高,,而且可以由其他微处理器,FPGA的发展速度也相当快。

Xilinx公司的早期产品XC2000、XC3000系列已经淘汰,XC4000系列也已进入淘汰行列。淘汰的主要原因是受当时工艺所限,密度较低,单位逻辑单元的成本较高,且使用的工作电压较高,功耗大。另外就是I/0接口的适应性差,无法满足目前低电压系统工作的要求。目前,两个新型系列Spartan和Virtex已经取代了早期产品。Spartan系列属于高密度低价FPGA,其中Spartan-Ⅱ(2.5V核心工作电压)和Spartan-ⅡE(1.8V核心工作电压)已成为主流产品,可适应5V、3.3Ⅴ、2.5V、1.8V、1,5Ⅴ等电源系统下的I/0接口。最现场可编程闸阵型号,DOUT主串串行输出从串从并,M2M1Mo配置前相关引脚是否上拉CCLK方向,数据宽度否是输出是否输人,当选择串行模式时,编程数据从PROM中以串行方式装人FPGA中,此时必须用有串行功能的PROM。主串装人模式电路如图7.4.12所示。当选择并行模式时,除了时钟信号外,还需提供其他读写控制信号,表7,4.5配置模式.

图7,4.12 主串模式电,FPGA不仅能够直接从PROM中读取配置数或单片机控制装入配置数据。

近年来,随着半导体工艺的进一步提高,,而且可以由其他微处理器,FPGA的发展速度也相当快。

Xilinx公司的早期产品XC2000、XC3000系列已经淘汰,XC4000系列也已进入淘汰行列。淘汰的主要原因是受当时工艺所限,密度较低,单位逻辑单元的成本较高,且使用的工作电压较高,功耗大。另外就是I/0接口的适应性差,无法满足目前低电压系统工作的要求。目前,两个新型系列Spartan和Virtex已经取代了早期产品。Spartan系列属于高密度低价FPGA,其中Spartan-Ⅱ(2.5V核心工作电压)和Spartan-ⅡE(1.8V核心工作电压)已成为主流产品,可适应5V、3.3Ⅴ、2.5V、1.8V、1,5Ⅴ等电源系统下的I/0接口。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

ma4p505-1072-30全局布线资源主要用于分配时钟信号和其他贯穿整个器件的高扇出信号。

这些布线资源分为主、次两级。主全局布线资源与提供高扇出时钟信号的专用输入引脚构成4个专用全局网络,每一个全局时钟网络可以驱动所有的CLB、IOB和RAM块的时钟引脚。有4个全局缓冲器分别驱动这4个主全局网络。

12根穿越时钟引脚的芯片顶部限制,所以比主布线资源使用更灵活。

信号的传输延时是限制器件工作速度的根本原因。在FPGA的设计过程中,由软件进行优化,确定电路布局的位置和线路选择,以减小传输延迟时间,提高工作速度。

FPGA编程简介,配置(编程)数据,由7.4.2节介绍看出,FPGA中的CLB、都是由它们相应的存储单元中的数据确IOB的功能和布线资源的连接,表7,4.3 几种芯片的配置数据量数据。将配置数据写人FPGA芯片后,该芯片便具有了所设计的功能。FPGA的规模不同,其所需配置数据量也不同,表7.4.3所示为Spartan-Ⅱ系列芯片的几个例子。

配置数据由FPGA开发软件①自动生成。开发系统将设计输人转换成网表文件,并自动对逻辑电路进行划分、布局和布线,然后按PROM格式生成配置数据流文件。可以用通用或专用编程器将配置数据写入PROM中。根据FPGA芯片型号所需配置数据量的多少选择相应容量的PROM。

配置数据的装入,由于SRAM在掉电后其内部的数据会丢失,所以基于SRAM的FPGA必须配置一个PROM芯片,用以存放FPGA的配置数据。每次上电后,FPGA可以自动将PROM中的配置数据装载到FPGA中,或通过控制FPGA相应的编程引脚,将配置数据装载到FPGA中。装载完成后,FPGA按照配置好的逻辑功能开始工作。

例如Xlllnx公司的1SE软件或其他第三方软件,明场可编程闸阵型号,配置数据量bit,当选择串行模式时,编程数据从PROM中以串行方式装人FPGA中,此时必须用有串行功能的PROM。主串装人模式电路如图7.4.12所示。当选择并行模式时,除了时钟信号外,还需提供其他读写控制信号。

表7,4.5配置模式,主串模式电,FPGA不仅能够直接从PROM中,读取配置数或单片机控制装入配置数据。

近年来,随着半导体工艺的进一步提高,,而且可以由其他微处理器,FPGA的发展速度也相当快。

Xilinx公司的早期产品XC2000、XC3000系列已经淘汰,XC4000系列也已进入淘汰行列。淘汰的主要原因是受当时工艺所限,密度较低,单位逻辑单元的成本较高,且使用的工作电压较高,功耗大。另外就是I/0接口的适应性差,无法满足目前低电压系统工作的要求。目前,两个新型系列Spartan和Virtex已经取代了早期产品。Spartan系列属于高密度低价FPGA,其中Spartan-Ⅱ(2.5V核心工作电压)和Spartan-ⅡE(1.8V核心工作电压)已成为主流产品,可适应5V、3.3Ⅴ、2.5V、1.8V、1,5Ⅴ等电源系统下的I/0接口。最现场可编程闸阵型号,DOUT主串串行输出从串从并,M2M1Mo配置前相关引脚是否上拉CCLK方向,数据宽度否是输出是否输人,当选择串行模式时,编程数据从PROM中以串行方式装人FPGA中,此时必须用有串行功能的PROM。主串装人模式电路如图7.4.12所示。当选择并行模式时,除了时钟信号外,还需提供其他读写控制信号,表7,4.5配置模式.

图7,4.12 主串模式电,FPGA不仅能够直接从PROM中读取配置数或单片机控制装入配置数据。

近年来,随着半导体工艺的进一步提高,,而且可以由其他微处理器,FPGA的发展速度也相当快。

Xilinx公司的早期产品XC2000、XC3000系列已经淘汰,XC4000系列也已进入淘汰行列。淘汰的主要原因是受当时工艺所限,密度较低,单位逻辑单元的成本较高,且使用的工作电压较高,功耗大。另外就是I/0接口的适应性差,无法满足目前低电压系统工作的要求。目前,两个新型系列Spartan和Virtex已经取代了早期产品。Spartan系列属于高密度低价FPGA,其中Spartan-Ⅱ(2.5V核心工作电压)和Spartan-ⅡE(1.8V核心工作电压)已成为主流产品,可适应5V、3.3Ⅴ、2.5V、1.8V、1,5Ⅴ等电源系统下的I/0接口。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公网安备44030402000607

公网安备44030402000607