lm3s9b81-iqc80c5���ʵ�ֱ���������������

����ʱ��:2020/1/16 17:33:20 ���ʴ���:1322

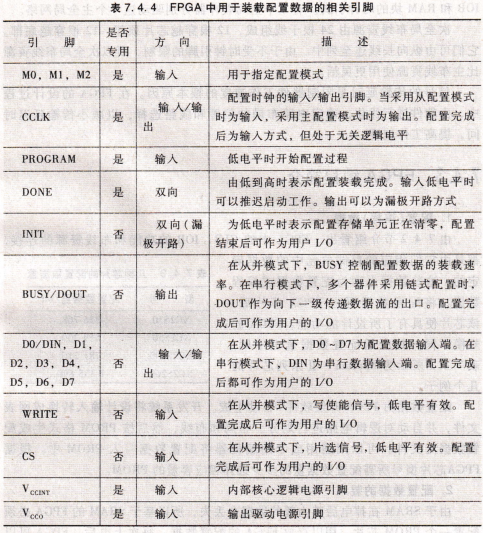

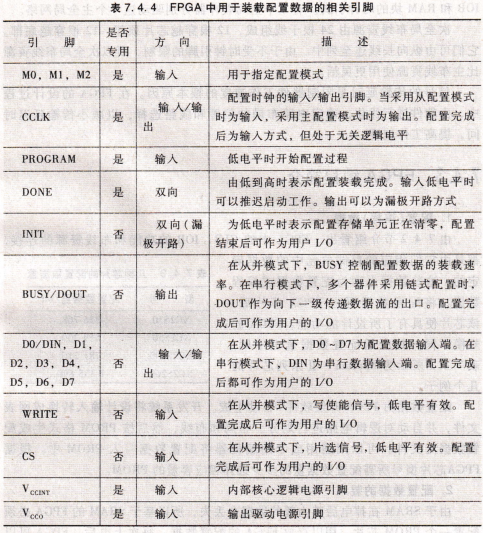

lm3s9b81-iqc80c5Ϊʵ����������,FGPA�ж�������Ӧ������,��Ҫ�������ʹ�ܡ��������롢���������״ָ̬ʾ��ʱ�ӵ��źš���7.4.4��ʾΪSpadan-��spartan-��E��Virtex����i1tex-Eϵ��FPGAоƬ����װ���������ݵ��������˵����

��7.4.4 FPGA������װ���������ݵ��������,����FPGA������ר������M2��M1��M0�����˲�ͬ������ƽʱ,���ѡ��һ������ģʽ��������װ�ˡ�����ģʽ���7.4.4��ʾ����ģʽ����FPGA�ڲ�������������ʱ���ź�CCLK������װ�б�����ݵ�PROM������ģʽ����Ҫ�ⲿ��·�ṩʱ���ź�������CCLK��װ�б�����ݵ�PROM��

�洢�������ӿɱ���������г��ɱ������,MO, M1, M2,����ָ������ģʽ,CCLK����ʱ�ӵ�����/������š������ô�����ģʽʱΪ����,����������ģʽʱΪ�����������ɺ�Ϊ���˷�ʽ,������������ƽPROGRAM,�͵�ƽʱ��ʼ���ù���DONE,�ɵ͵���ʱ��ʾ����װ����ɡ�

���˵͵�ƽʱ�����Ƴ������������������Ϊ©����·��ʽΪ�͵�ƽʱ��ʾ���ô洢��Ԫ��������,���ý��������Ϊ�û�1/o,�ڴӲ�ģʽ��,BUSY�����������ݵ�װ�����ʡ��ڴ���ģʽ��,�������������ʽ����ʱ,DOUT��Ϊ����һ�������������ij���,�������ɺ����Ϊ�û���I/0.

�ڴӲ�ģʽ��,DO~D7Ϊ�����������˶ˡ��ڴ���ģʽ��,DINΪ�����������˶ˡ�������ɺ���Ϊ�û���I/o,�ڴӲ�ģʽ��,дʹ���ź�,�͵�ƽ��Ч��������ɺ����Ϊ�û���I/o,�ڴӲ�ģʽ��,Ƭѡ�ź�,�͵�ƽ��Ч��������ɺ����Ϊ�û���,�ڲ���������Դ����,���������Դ�����ֹ���Ƶ�ʴ�200 MHz��

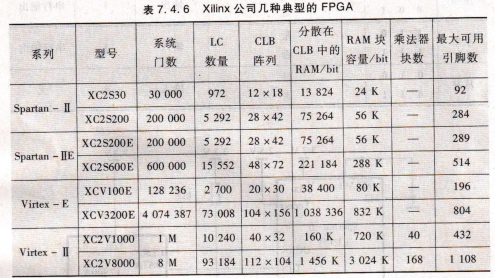

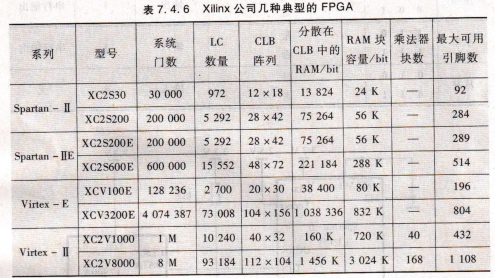

Virtexϵ��Ϊ���ܶȡ������ܲ�Ʒ�����Т�irtex-E(1.8�����Ĺ�����ѹ)��Virtex-��(1.5V���Ĺ�����ѹ)Ҳ����Ϊ������Ʒ����irtex-���ڲ�ʱ�ӹ���Ƶ�ʿɴ�420 MHz,���ڲ��Ѽ�����18��18�˷�������7.4,6��ʾΪ���ֵ��͵�FPGA��Ʒ��ģ���ɱ��п���,XC2��8000�������������Ѵ�1108����

Xilinx��˾���ֵ��͵�FPGA,ʵ��������Ԫ����֯��ʽ��˾��,AlteraҲ�����Ŀɱ����������Ӧ��֮һ,����ԭ��������Xilinx��˾��FPGA�����ǵ���Ҫ������ڲ����Ӳ��߷�ʽ��ͬ��Altera��FPGA����������FPGA������,����������Ԫ�϶�,һ��Ϊ8�����ϡ�������ʽ�����ݺύ���Ŀ��ٻ���ͨ��(Fast~Track),û���ÿ��ؾ���,�źŵĴ�����ʱһ���ԽϺá�Altera FPGA�IJ�Ʒ��Ҫ��FLE����APEX��straux��cyclone��MAXII�ȡ�����FLEX��APEX����20����90���ĩ�IJ�Ʒ,Ŀǰ��stratix��Cycloneȡ����

spanan-��ϵ�е�FPGA��,1��CLB�м������м���LUT?

����������?1��CLB��ʵ�ֶ�������������������?

7,4.4 �ɱ�̿��ص�(ͼ7.3.4)�Ϳɱ�̿��ؾ����е����ӵ��к�����?

7,4.5 Ϊʲô��FPGA���ɵ�����ϵͳ��Ҫ���һ��PROM��EPROM?�洢�������ӿɱ���������ֳ��ɱ��������,������������.

������Ψ�жȿƼ�����˾http://wydkj.51dzw.com/

lm3s9b81-iqc80c5Ϊʵ����������,FGPA�ж�������Ӧ������,��Ҫ�������ʹ�ܡ��������롢���������״ָ̬ʾ��ʱ�ӵ��źš���7.4.4��ʾΪSpadan-��spartan-��E��Virtex����i1tex-Eϵ��FPGAоƬ����װ���������ݵ��������˵����

��7.4.4 FPGA������װ���������ݵ��������,����FPGA������ר������M2��M1��M0�����˲�ͬ������ƽʱ,���ѡ��һ������ģʽ��������װ�ˡ�����ģʽ���7.4.4��ʾ����ģʽ����FPGA�ڲ�������������ʱ���ź�CCLK������װ�б�����ݵ�PROM������ģʽ����Ҫ�ⲿ��·�ṩʱ���ź�������CCLK��װ�б�����ݵ�PROM��

�洢�������ӿɱ���������г��ɱ������,MO, M1, M2,����ָ������ģʽ,CCLK����ʱ�ӵ�����/������š������ô�����ģʽʱΪ����,����������ģʽʱΪ�����������ɺ�Ϊ���˷�ʽ,������������ƽPROGRAM,�͵�ƽʱ��ʼ���ù���DONE,�ɵ͵���ʱ��ʾ����װ����ɡ�

���˵͵�ƽʱ�����Ƴ������������������Ϊ©����·��ʽΪ�͵�ƽʱ��ʾ���ô洢��Ԫ��������,���ý��������Ϊ�û�1/o,�ڴӲ�ģʽ��,BUSY�����������ݵ�װ�����ʡ��ڴ���ģʽ��,�������������ʽ����ʱ,DOUT��Ϊ����һ�������������ij���,�������ɺ����Ϊ�û���I/0.

�ڴӲ�ģʽ��,DO~D7Ϊ�����������˶ˡ��ڴ���ģʽ��,DINΪ�����������˶ˡ�������ɺ���Ϊ�û���I/o,�ڴӲ�ģʽ��,дʹ���ź�,�͵�ƽ��Ч��������ɺ����Ϊ�û���I/o,�ڴӲ�ģʽ��,Ƭѡ�ź�,�͵�ƽ��Ч��������ɺ����Ϊ�û���,�ڲ���������Դ����,���������Դ�����ֹ���Ƶ�ʴ�200 MHz��

Virtexϵ��Ϊ���ܶȡ������ܲ�Ʒ�����Т�irtex-E(1.8�����Ĺ�����ѹ)��Virtex-��(1.5V���Ĺ�����ѹ)Ҳ����Ϊ������Ʒ����irtex-���ڲ�ʱ�ӹ���Ƶ�ʿɴ�420 MHz,���ڲ��Ѽ�����18��18�˷�������7.4,6��ʾΪ���ֵ��͵�FPGA��Ʒ��ģ���ɱ��п���,XC2��8000�������������Ѵ�1108����

Xilinx��˾���ֵ��͵�FPGA,ʵ��������Ԫ����֯��ʽ��˾��,AlteraҲ�����Ŀɱ����������Ӧ��֮һ,����ԭ��������Xilinx��˾��FPGA�����ǵ���Ҫ������ڲ����Ӳ��߷�ʽ��ͬ��Altera��FPGA����������FPGA������,����������Ԫ�϶�,һ��Ϊ8�����ϡ�������ʽ�����ݺύ���Ŀ��ٻ���ͨ��(Fast~Track),û���ÿ��ؾ���,�źŵĴ�����ʱһ���ԽϺá�Altera FPGA�IJ�Ʒ��Ҫ��FLE����APEX��straux��cyclone��MAXII�ȡ�����FLEX��APEX����20����90���ĩ�IJ�Ʒ,Ŀǰ��stratix��Cycloneȡ����

spanan-��ϵ�е�FPGA��,1��CLB�м������м���LUT?

����������?1��CLB��ʵ�ֶ�������������������?

7,4.4 �ɱ�̿��ص�(ͼ7.3.4)�Ϳɱ�̿��ؾ����е����ӵ��к�����?

7,4.5 Ϊʲô��FPGA���ɵ�����ϵͳ��Ҫ���һ��PROM��EPROM?�洢�������ӿɱ���������ֳ��ɱ��������,������������.

������Ψ�жȿƼ�����˾http://wydkj.51dzw.com/

�������

�������

- TMX320C6202GJL �ź�Ƶ�ʿ���Ϊ

- BC868-16��ʽ��ѹ��

- MIC5842YWM ±������������

- 74ACT11244DW����ܵ��ڲ��ṹ����

- 10009542 ���ͨʽת�ٴ�����

- AC20 �������뵼������ʶ��ǩ֮��

- QG6700PXH ��Ȧ�и�����߲�����Ӧ��

- BKAE2-A143-32301 ��Ҫ������

- U4089B-MFN CMS�����ֹ�����ʽ

- HMC643 ILS���ջ��ڰ�������

�Ƽ���������

�Ƽ���������

- ����ѹ���ṩ

- ��ʼ��ʱ����ʹ��LM385��Ϊ����HIN202EC... [��ϸ]

- ��һ������8ϵ���콢оƬӦ���о�

- ��Դ��ͨ�˲���(RC4558DN)Ӧ�����

- WTC6216����ʽ�������Ӧ

- ��Ƕ��ʽ�洢��ASIC��SoC����ص�����

- 16V��8A Silent Switcher

- ����ƥ���˲�оƬ

- ��ý��Э������SM501��Ƕ��ʽϵͳ�е�Ӧ��

- ����IEEE802.11b��EPA�¶ȱ�����

- QUICCEngine�������ƶ�IP�������

- SoC���������IJ�ҵ����

- MPC8xxϵ�д�������Ƕ��ʽϵͳ��Դ���

- dsPIC�����ڽ�����Ƶ�����е�Ӧ���о�

��������44030402000607

��������44030402000607