高成本、高性能数字⒏-CMOS工艺

发布时间:2016/6/19 18:48:05 访问次数:514

高成本、高性能数字Bi£MOS工艺需要确保CMOs器件和双极型器件的性能均达到单独制造时的水平。 EPM570T100I5N可以采用两种基本的方法修正P阱Bi-CMOS工艺,额外增加3个掩膜过程;(2)修正双阱Bi£MOs工艺,额外增加3~4个掩膜过程。

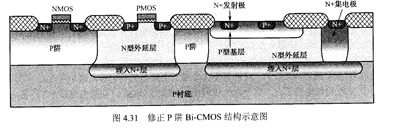

P阱CMOs工艺如图4.31所示,这种工艺通过采用了P衬底N外延,在P阱之外的区域制作了重掺杂的N型埋层,减小了集电极电阻,这些重掺杂的N+埋层区成为标准的埋入集电区,形成双极型晶体管的集电极,这项工艺有时又称为SBCBi-CMOS(Standard-Buried-Collcctor)工艺。在Bi£MOs工艺中使用N+埋层具有3个关键性的优点:(1)降低集电极电阻Rc的值;(2)降低器件对CMOs闩锁效应的敏感性;(3)通过以N型外延层取代P型外延层来改善器件的抗闩锁特性。P阱用以在相邻的集电极之间提供双极结区隔离。向标准P阱CMOs工艺增加的3个额外的掩膜步骤用以形成N+型埋层、集电极深N+层和P基极区。

高成本、高性能数字Bi£MOS工艺需要确保CMOs器件和双极型器件的性能均达到单独制造时的水平。 EPM570T100I5N可以采用两种基本的方法修正P阱Bi-CMOS工艺,额外增加3个掩膜过程;(2)修正双阱Bi£MOs工艺,额外增加3~4个掩膜过程。

P阱CMOs工艺如图4.31所示,这种工艺通过采用了P衬底N外延,在P阱之外的区域制作了重掺杂的N型埋层,减小了集电极电阻,这些重掺杂的N+埋层区成为标准的埋入集电区,形成双极型晶体管的集电极,这项工艺有时又称为SBCBi-CMOS(Standard-Buried-Collcctor)工艺。在Bi£MOs工艺中使用N+埋层具有3个关键性的优点:(1)降低集电极电阻Rc的值;(2)降低器件对CMOs闩锁效应的敏感性;(3)通过以N型外延层取代P型外延层来改善器件的抗闩锁特性。P阱用以在相邻的集电极之间提供双极结区隔离。向标准P阱CMOs工艺增加的3个额外的掩膜步骤用以形成N+型埋层、集电极深N+层和P基极区。

上一篇:低成本、中速数字⒏-CMOs工艺

上一篇:双阱Bi-CMOs工艺

公网安备44030402000607

公网安备44030402000607