VI-JWP-IX 动态随机存取存储器DRAM的缺点

发布时间:2020/2/10 20:13:33 访问次数:1827

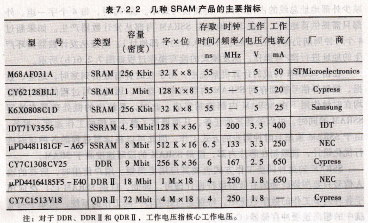

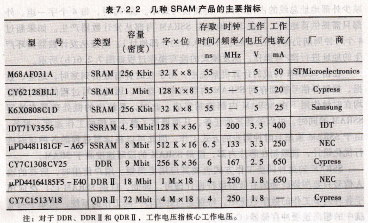

VI-JWP-IX表7.2.2 几种SRAM产品的主要指标

注:对于DDR、DDR Ⅱ和QDR Ⅱ,工作电压指核心工作电压。

动态随机存取存储器,DRAM存储单元

图7.2.2所示的SRAM存储单元由6个MOs管构成,所用的管子数目多、功耗大,集成度受到限制,动态随机存取存储器DRAM克服了这些缺点。DRAM的存储单元由一个MOs管和一个容量较小电容器构成,如图7.2.7中点画线框内所示。它存储数据的原理是电容器的电荷存储效应。当电容C充有电荷、呈现高电压时,相当于存有1值,反之为0值。MOs管T相当于一个开关,当行选择线为高电平时,T导通,C与位线连通,反之则断开。由于电路中存在漏电流,电容器上存储的数据(电荷)不能长久保存,因此必须定期给电容补充电荷,以免存储数据丢失,这种操作称为刷新①或再生。

写操作时,行选线X为高电平,T导通,电容器C与位线B连通。同时读写控制信号WE为低电平,输入缓冲器被选通,数据D1经缓冲器和位线写人存储单元(外部输入/输出引脚上的数据经列选通电路送至D1。图中未画列选通电路)。如果D1为1,则向电容器充电,反之电容器放电。未选通的缓冲器呈高阻态。

读操作时,行选线X为高电平,T导通,电容器C与位线B连通。此时刷新系Refresh的译称.

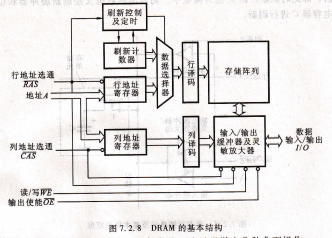

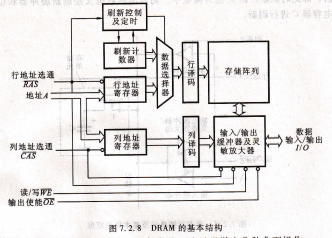

列两个地址寄存器。行、列地址分别由行地址选通信号RAs①和列地址选通信号CAs②控制,送人各自的寄存器。此外,DRAM内部还设有刷新计数器和刷新控制及定时电路,由此可以自动产生行地址进行刷新。

图7.2.8 DRAM的基本结构,DRAM的操作方式比SRAM要复杂些,这里只举出几种典型操作,读/写操作.

读/写操作时,首先RAs和CAS先后变为低电平,将行和列地址分别送入相应地址寄存器。然后在读写控制信号WE作用下完成读/写操作。读操作时,输出使能0E应为低电平。操作时序如图7.2.9(a)所示。

页模式操作,所谓“页”是指同一行的所有列构成的存储单元。页模式下的读写操作与一般读写操作的差别在于不改变行地址,而只改变列地址。但行地址选择RAS必须始终保持低电平。页模式可以显著提高读写速度,其读操作时序如图7.2.9(b)所示。

RAs只刷新操作,该操作只刷新行地址指定行的所有存储单元,不进行任何实际的读写操作。在整个操作周期CAs要保持高电平,其时序如图7.2.9(c)所示。该操作一次只刷新一行,且需要外部地址计数器提供刷新地址。

系Row Address strobe的缩写。

系Column Address strobe的缩写。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

VI-JWP-IX表7.2.2 几种SRAM产品的主要指标

注:对于DDR、DDR Ⅱ和QDR Ⅱ,工作电压指核心工作电压。

动态随机存取存储器,DRAM存储单元

图7.2.2所示的SRAM存储单元由6个MOs管构成,所用的管子数目多、功耗大,集成度受到限制,动态随机存取存储器DRAM克服了这些缺点。DRAM的存储单元由一个MOs管和一个容量较小电容器构成,如图7.2.7中点画线框内所示。它存储数据的原理是电容器的电荷存储效应。当电容C充有电荷、呈现高电压时,相当于存有1值,反之为0值。MOs管T相当于一个开关,当行选择线为高电平时,T导通,C与位线连通,反之则断开。由于电路中存在漏电流,电容器上存储的数据(电荷)不能长久保存,因此必须定期给电容补充电荷,以免存储数据丢失,这种操作称为刷新①或再生。

写操作时,行选线X为高电平,T导通,电容器C与位线B连通。同时读写控制信号WE为低电平,输入缓冲器被选通,数据D1经缓冲器和位线写人存储单元(外部输入/输出引脚上的数据经列选通电路送至D1。图中未画列选通电路)。如果D1为1,则向电容器充电,反之电容器放电。未选通的缓冲器呈高阻态。

读操作时,行选线X为高电平,T导通,电容器C与位线B连通。此时刷新系Refresh的译称.

列两个地址寄存器。行、列地址分别由行地址选通信号RAs①和列地址选通信号CAs②控制,送人各自的寄存器。此外,DRAM内部还设有刷新计数器和刷新控制及定时电路,由此可以自动产生行地址进行刷新。

图7.2.8 DRAM的基本结构,DRAM的操作方式比SRAM要复杂些,这里只举出几种典型操作,读/写操作.

读/写操作时,首先RAs和CAS先后变为低电平,将行和列地址分别送入相应地址寄存器。然后在读写控制信号WE作用下完成读/写操作。读操作时,输出使能0E应为低电平。操作时序如图7.2.9(a)所示。

页模式操作,所谓“页”是指同一行的所有列构成的存储单元。页模式下的读写操作与一般读写操作的差别在于不改变行地址,而只改变列地址。但行地址选择RAS必须始终保持低电平。页模式可以显著提高读写速度,其读操作时序如图7.2.9(b)所示。

RAs只刷新操作,该操作只刷新行地址指定行的所有存储单元,不进行任何实际的读写操作。在整个操作周期CAs要保持高电平,其时序如图7.2.9(c)所示。该操作一次只刷新一行,且需要外部地址计数器提供刷新地址。

系Row Address strobe的缩写。

系Column Address strobe的缩写。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公网安备44030402000607

公网安备44030402000607