XC2S400E-7FGG676I 存储器和时序逻辑器件

发布时间:2020/2/8 13:24:55 访问次数:1355

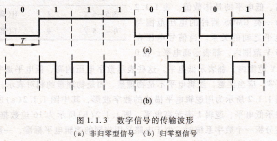

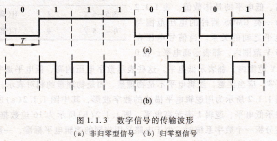

XC2S400E-7FGG676I数字波形的两种类型,数字波形是逻辑电平对时间的图形表示。数字信号有两种传输波形,一种是非归零型,另一种是归零型。在图1.1.3中,一定的时间间隔r,称为1位(1 bit),或者一拍。如果在一个时间拍内用高电平代表1,低电平代表0,称为非归零型,如图1.1.3(a)所示。如果在一个时间拍内有脉冲代表1,无脉冲代表0,称为归零型,如图1.1.3(b)所示。两者的区别在于,非归零型信号在一个时间拍内不归零,而归零型信号在一个时间拍内会归零。只有作为时序控制信号使用的时钟脉冲是归零型,除此之外的大多数数字信号基本都是非归零型,非归零型信号使用较为广泛。

图1.1.3 数字信号的传输波形,(a)非归零型信号 (b)归零型信号

数字信号只有两个取值,故称为二值信号,数字波形又称为二值位形图。

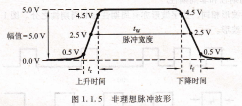

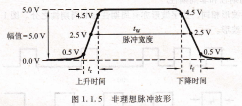

非归零信号的每位数据占用一个位时间。每秒钟所传输数据的位数称为数据率程,分别用上升时间rr和下降时间莎r描述,如图1.1.5所示。将脉冲幅值的10%到90%时所经历的时间称为上升时间rr。下降时间则相反,从脉冲幅值的90%下降到10%时所经历的时间称为下降时间tf。将脉冲幅值的50%的两个时间点所跨越的时间称为脉冲宽度Jw,对于不同类型的器件和电路,其上升和下降时间各不相同。一般数字信号上升和下降时间的典型值约为几纳秒(ns)。

50V 4.5V幅值=⒌0V,2.5V脉冲宽度上升时间,下降时间.

图1.1.5 非理想脉冲波形

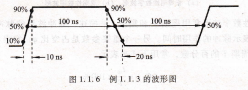

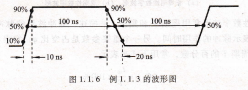

例1.1.3 试绘出一脉冲波形,设它的占空比为50%,脉冲宽度为100 ns,上升时间为10 ns,而下降时间为20 ns。

解:根据题意,所绘出的脉冲波形如图1.1.6所示。

图1.1.6 例1.1.3的波形图

本书所用的数字波形大多数将画成理想波形。实际上,每一波形均有上升时间和下降时间。由于rr和Jf与脉冲宽度的时间相比非常小,则不必在每一波形上表示出来。画波形的目的只是为了知道高、低电平所经历的时间。

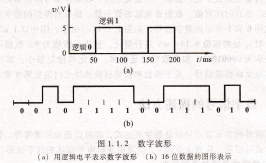

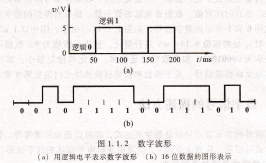

时序图,在数字电路中,常用时序图或称为脉冲波形图,来分析时序电路的逻辑功能。表明各信号之间时序关系的波形图称为时序图。图1.1.2所示为一典型的时序图。图中CP为时钟脉冲信号,它是数字系统中的时间参考信号。地址线、片选和数据写入等信号亦示于图1.1.2中。关于时序图中各个波形的具体作用,将在后续章节中介绍。通常数字集成电路,例如存储器和时序逻辑器件等均须附有时序图,以便于进行数字系统的分析、设计和应用。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

XC2S400E-7FGG676I数字波形的两种类型,数字波形是逻辑电平对时间的图形表示。数字信号有两种传输波形,一种是非归零型,另一种是归零型。在图1.1.3中,一定的时间间隔r,称为1位(1 bit),或者一拍。如果在一个时间拍内用高电平代表1,低电平代表0,称为非归零型,如图1.1.3(a)所示。如果在一个时间拍内有脉冲代表1,无脉冲代表0,称为归零型,如图1.1.3(b)所示。两者的区别在于,非归零型信号在一个时间拍内不归零,而归零型信号在一个时间拍内会归零。只有作为时序控制信号使用的时钟脉冲是归零型,除此之外的大多数数字信号基本都是非归零型,非归零型信号使用较为广泛。

图1.1.3 数字信号的传输波形,(a)非归零型信号 (b)归零型信号

数字信号只有两个取值,故称为二值信号,数字波形又称为二值位形图。

非归零信号的每位数据占用一个位时间。每秒钟所传输数据的位数称为数据率程,分别用上升时间rr和下降时间莎r描述,如图1.1.5所示。将脉冲幅值的10%到90%时所经历的时间称为上升时间rr。下降时间则相反,从脉冲幅值的90%下降到10%时所经历的时间称为下降时间tf。将脉冲幅值的50%的两个时间点所跨越的时间称为脉冲宽度Jw,对于不同类型的器件和电路,其上升和下降时间各不相同。一般数字信号上升和下降时间的典型值约为几纳秒(ns)。

50V 4.5V幅值=⒌0V,2.5V脉冲宽度上升时间,下降时间.

图1.1.5 非理想脉冲波形

例1.1.3 试绘出一脉冲波形,设它的占空比为50%,脉冲宽度为100 ns,上升时间为10 ns,而下降时间为20 ns。

解:根据题意,所绘出的脉冲波形如图1.1.6所示。

图1.1.6 例1.1.3的波形图

本书所用的数字波形大多数将画成理想波形。实际上,每一波形均有上升时间和下降时间。由于rr和Jf与脉冲宽度的时间相比非常小,则不必在每一波形上表示出来。画波形的目的只是为了知道高、低电平所经历的时间。

时序图,在数字电路中,常用时序图或称为脉冲波形图,来分析时序电路的逻辑功能。表明各信号之间时序关系的波形图称为时序图。图1.1.2所示为一典型的时序图。图中CP为时钟脉冲信号,它是数字系统中的时间参考信号。地址线、片选和数据写入等信号亦示于图1.1.2中。关于时序图中各个波形的具体作用,将在后续章节中介绍。通常数字集成电路,例如存储器和时序逻辑器件等均须附有时序图,以便于进行数字系统的分析、设计和应用。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公网安备44030402000607

公网安备44030402000607