sPI总线数据/时钟时序

发布时间:2016/7/18 20:26:59 访问次数:958

sCLK(sPI Clock,串行时钟信号):串行时钟信号是主器件的输出和从器件的输入,用于HMC1020LP4E同步主器件和从器件之间在MOsI和MIsO线上的串行数据传输。当主器件启动一次数据传输时,自动产生8个sCLK时钟周期信号给从机。在SCLK的每个跳变处(上升沿或下降沿)移出一位数据。所以,一次数据传输可以传输一个字节的数据。

sCLK、MOsI和MIsO通常和两个或更多sPI器件连接在一起。数据通过MOsI由主机传送到从机,通过MIs0由从机传送到主机。sCLK信号在主模式时为输出,在从模式时为输入。

ss(slavc select,从机选择信号):这是一个输入信号,主器件用它来选择处于从模式的sPI模块。主模式和从模式下,ss的使用方法不同。在主模式下,sPI接口只能有一个主机,不存在主机选择问题,该模式下ss不是必需的。主模式下通常将主机的ss引脚通过10kΩ的

电阻上拉高电平。每个从机的蕊接主机的I/o口,由主机控制电平高低,以便主机选择从机。在从模式下,不管发送还是接收,ss信号必须有效,因此在一次数据传输开始之前必须将雨置为低电平。sPI主机可以使用V0口选择一个SPI器件作为当前的从机。

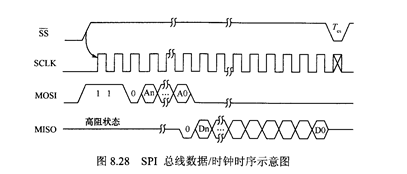

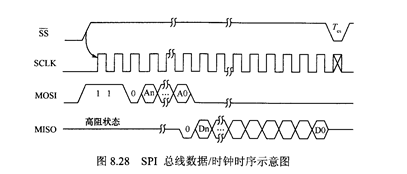

sⅡ系统数据交换的时序信号定义如图8,28所示,在雨信号有效后,sPI芯片被选中,在sCK的控制下,数据传送在MOSI/MIs0总线上进行,从高位至低位逐位传送。8位送完,蕊信号复位,传送结束。

sCLK(sPI Clock,串行时钟信号):串行时钟信号是主器件的输出和从器件的输入,用于HMC1020LP4E同步主器件和从器件之间在MOsI和MIsO线上的串行数据传输。当主器件启动一次数据传输时,自动产生8个sCLK时钟周期信号给从机。在SCLK的每个跳变处(上升沿或下降沿)移出一位数据。所以,一次数据传输可以传输一个字节的数据。

sCLK、MOsI和MIsO通常和两个或更多sPI器件连接在一起。数据通过MOsI由主机传送到从机,通过MIs0由从机传送到主机。sCLK信号在主模式时为输出,在从模式时为输入。

ss(slavc select,从机选择信号):这是一个输入信号,主器件用它来选择处于从模式的sPI模块。主模式和从模式下,ss的使用方法不同。在主模式下,sPI接口只能有一个主机,不存在主机选择问题,该模式下ss不是必需的。主模式下通常将主机的ss引脚通过10kΩ的

电阻上拉高电平。每个从机的蕊接主机的I/o口,由主机控制电平高低,以便主机选择从机。在从模式下,不管发送还是接收,ss信号必须有效,因此在一次数据传输开始之前必须将雨置为低电平。sPI主机可以使用V0口选择一个SPI器件作为当前的从机。

sⅡ系统数据交换的时序信号定义如图8,28所示,在雨信号有效后,sPI芯片被选中,在sCK的控制下,数据传送在MOSI/MIs0总线上进行,从高位至低位逐位传送。8位送完,蕊信号复位,传送结束。

热门点击

热门点击

- 外部中断0中断请求标志位。

- TDDB效应的击穿机制

- 轻掺杂源漏(LDD)

- 等比例缩小的3个规则

- 界面态的产生过程

- ADC0809工作原理

- 低势垒高度的欧姆接触

- MOs管的实际版图

- MOsFET的阈值电压

- 说明动态RAM和静态RAM的主要区别

推荐技术资料

推荐技术资料

- 硬盘式MP3播放器终级改

- 一次偶然的机会我结识了NE0 2511,那是一个远方的... [详细]

公网安备44030402000607

公网安备44030402000607