静态基本存储电路

发布时间:2016/7/7 21:21:47 访问次数:785

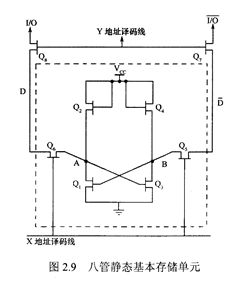

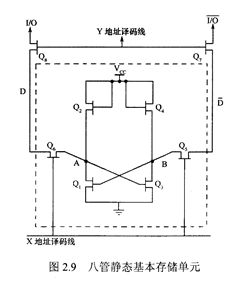

MOS触发器静态RAM是用MOs管作为基本记忆元件。图2.9是一个NMOS八管静态基本存储单元电路。ADIS16334BMLZ 输入信号主要有X地址译码线和Y地址译码线,统称为字线,I/o和I/O是 与外部连接的数据信号线,可输入,也可作为输出,D和D统称为位线。Q1~%组成静态触发器,Ql、Q为控制管,Q2、%为负载。触发器有两个不同的稳定状态:Ql截止时A=“1”(高电平),它使Q3导通,于是B=“0”(低电平),而B=“0”又保证了Q1截止。所以,这种状态是稳定的。同样,Ql导电,α截止的状态也是互相保证而稳定的。因此,可以用这两种不同状态分别表示“1”或“0”。

当X译码输出线为高电平时,则Q5~Q6导通,A、B端就与位线D和D相连;当这个电路被选中时,相应的Y译码输出也是高电平,Q7、Q:也是导通的,于是,存储器内部的D和D就与外部的输入/输出电路I/O及I/o相通。当写入时,写入信号自I/O和I/o线输入,若要写“1”,则I/o线为“l”,而I/o线为“0”。它们通过Q:、Q7以及Q6、Q5分别与A端和B端相连,使A=“1”,B=“0”,这样 Q3导通、Q1截止,相当于把输入电荷存储于Q1和α的栅极。当输入信号及地址选择信号消失

后,Q5、Q6、Q7、Q:都截止,由于存储单元有电源和两负载管,可以不断地向栅极补充电荷,所以靠两个反相器的交叉控制,只要不掉电就能保持写入的信号“1”,而不用再刷新。若要写入“0”,原理一样。

MOS触发器静态RAM是用MOs管作为基本记忆元件。图2.9是一个NMOS八管静态基本存储单元电路。ADIS16334BMLZ 输入信号主要有X地址译码线和Y地址译码线,统称为字线,I/o和I/O是 与外部连接的数据信号线,可输入,也可作为输出,D和D统称为位线。Q1~%组成静态触发器,Ql、Q为控制管,Q2、%为负载。触发器有两个不同的稳定状态:Ql截止时A=“1”(高电平),它使Q3导通,于是B=“0”(低电平),而B=“0”又保证了Q1截止。所以,这种状态是稳定的。同样,Ql导电,α截止的状态也是互相保证而稳定的。因此,可以用这两种不同状态分别表示“1”或“0”。

当X译码输出线为高电平时,则Q5~Q6导通,A、B端就与位线D和D相连;当这个电路被选中时,相应的Y译码输出也是高电平,Q7、Q:也是导通的,于是,存储器内部的D和D就与外部的输入/输出电路I/O及I/o相通。当写入时,写入信号自I/O和I/o线输入,若要写“1”,则I/o线为“l”,而I/o线为“0”。它们通过Q:、Q7以及Q6、Q5分别与A端和B端相连,使A=“1”,B=“0”,这样 Q3导通、Q1截止,相当于把输入电荷存储于Q1和α的栅极。当输入信号及地址选择信号消失

后,Q5、Q6、Q7、Q:都截止,由于存储单元有电源和两负载管,可以不断地向栅极补充电荷,所以靠两个反相器的交叉控制,只要不掉电就能保持写入的信号“1”,而不用再刷新。若要写入“0”,原理一样。

上一篇:MOs型RAM

公网安备44030402000607

公网安备44030402000607