Bi-MOS

发布时间:2015/11/13 21:35:30 访问次数:818

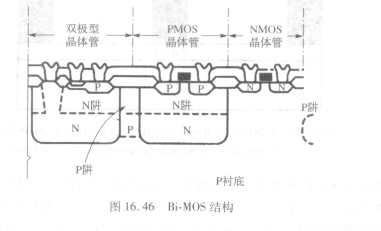

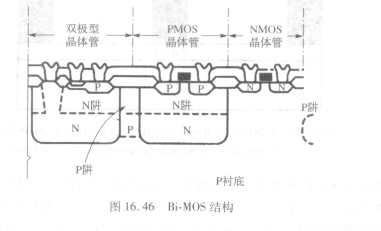

双极型和CMOS晶体管与它们各自电路的优点汇集在Bi-MOS(或Bi-CMOS)电路中。 OL25TAD108图16. 46所示的电路是和存储器相关的双极型、P沟道型和N沟道型晶体管(见第17章)。CMOS低功耗的特点被用在逻辑电路和存储器电路中,双极型电路速度高的特性则被用在信号电路中挖。这些电路体现了对工艺的极大挑战:更大的芯片尺寸,更小的器件尺寸和大量的工艺步骤。

绝缘体上硅隔离

绝缘体上硅( SOI)技术是在形成CMOS和Bi-CMOS时,在绝缘衬底上淀积一层薄EPI外延层(见第12章)。消除电导性衬底可以将漏电流问题和闩锁效应问题最小化13J.

片上系统

创新通常是由新的需要驱动的。一种现行的半导体电路将自己进化到手持式无线器件爆发,例如,移动电话、智能电话和平板电脑,它们被称为片上系统( System on a Chip,SoC)。这些器件是真正的计算机,并要求如此多功能却只占据很小的空间。这些器件包括处理器、图像接口、数据管理、无线连接性、存储器等。幸运的是,微芯片制造工艺酌进步允许这些“百万”级芯片被制造出来。

减少空间的要求也已涉及到封装层次。单芯片能被封装的略比芯片本身大一点。新的三维封装方法致力于将多个芯片封装在一个封装体内(见第18章)。

双极型和CMOS晶体管与它们各自电路的优点汇集在Bi-MOS(或Bi-CMOS)电路中。 OL25TAD108图16. 46所示的电路是和存储器相关的双极型、P沟道型和N沟道型晶体管(见第17章)。CMOS低功耗的特点被用在逻辑电路和存储器电路中,双极型电路速度高的特性则被用在信号电路中挖。这些电路体现了对工艺的极大挑战:更大的芯片尺寸,更小的器件尺寸和大量的工艺步骤。

绝缘体上硅隔离

绝缘体上硅( SOI)技术是在形成CMOS和Bi-CMOS时,在绝缘衬底上淀积一层薄EPI外延层(见第12章)。消除电导性衬底可以将漏电流问题和闩锁效应问题最小化13J.

片上系统

创新通常是由新的需要驱动的。一种现行的半导体电路将自己进化到手持式无线器件爆发,例如,移动电话、智能电话和平板电脑,它们被称为片上系统( System on a Chip,SoC)。这些器件是真正的计算机,并要求如此多功能却只占据很小的空间。这些器件包括处理器、图像接口、数据管理、无线连接性、存储器等。幸运的是,微芯片制造工艺酌进步允许这些“百万”级芯片被制造出来。

减少空间的要求也已涉及到封装层次。单芯片能被封装的略比芯片本身大一点。新的三维封装方法致力于将多个芯片封装在一个封装体内(见第18章)。

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607