CMOS外延

发布时间:2015/11/8 18:16:25 访问次数:878

CMOS外延:到20世纪70年代后期,外延膜的主要应用是作为双极型晶体管的集电极,HCPL-0721该技术为器件工作和灵活的隔离相邻器件提供了高质量的衬底(见第16章)。,较新的或更主要的应用是用于CMOS电路的晶圆。CMOS电路中存在称为“闩锁”(latch-up)效应的问题,该问题提出了对外延层的需要(见第16章)。解决方案是在p+衬底f二做一层P型外延。

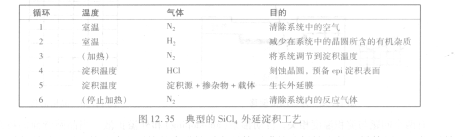

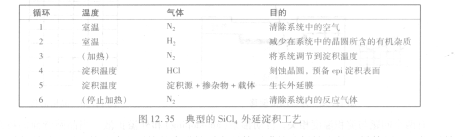

外延工艺:典型的外延工艺开始前,对晶圆表面进行彻底、严格地清洗,然后将晶圆装入淀积反应室内。在淀积反应室肉,通过一系列步骤来保证正确的淀积薄膜。图12.35给出了一个典型的SiCI。的外延工艺。起始的步骤是:对晶圆表面进行气相清洗。清洗之后进行淀积,并伴随着循环的清洗冷却。在所有的步骤中温度和气体的流量是工艺控制的关键.

图12. 35 典型的SiCl。外延淀积工艺

选择性外延硅:外延淀积系统的先进性引发了外延膜的选择性生长。尽管用于双极型晶体管和CMOS衬底的外延膜淀积在整个晶圆上,但在选择性生长中,它们是通过二氧化硅或氮化硅膜进行生长的。晶圆被放置在反应室内,外延膜直接生长在暴露孔底部的硅上(见图12. 36)。薄膜生长时,它会与晶圆表面下晶体形成定向。这种结构的优点是在外延区域形成的器件由氧化物或氮化物相互隔离。

CMOS外延:到20世纪70年代后期,外延膜的主要应用是作为双极型晶体管的集电极,HCPL-0721该技术为器件工作和灵活的隔离相邻器件提供了高质量的衬底(见第16章)。,较新的或更主要的应用是用于CMOS电路的晶圆。CMOS电路中存在称为“闩锁”(latch-up)效应的问题,该问题提出了对外延层的需要(见第16章)。解决方案是在p+衬底f二做一层P型外延。

外延工艺:典型的外延工艺开始前,对晶圆表面进行彻底、严格地清洗,然后将晶圆装入淀积反应室内。在淀积反应室肉,通过一系列步骤来保证正确的淀积薄膜。图12.35给出了一个典型的SiCI。的外延工艺。起始的步骤是:对晶圆表面进行气相清洗。清洗之后进行淀积,并伴随着循环的清洗冷却。在所有的步骤中温度和气体的流量是工艺控制的关键.

图12. 35 典型的SiCl。外延淀积工艺

选择性外延硅:外延淀积系统的先进性引发了外延膜的选择性生长。尽管用于双极型晶体管和CMOS衬底的外延膜淀积在整个晶圆上,但在选择性生长中,它们是通过二氧化硅或氮化硅膜进行生长的。晶圆被放置在反应室内,外延膜直接生长在暴露孔底部的硅上(见图12. 36)。薄膜生长时,它会与晶圆表面下晶体形成定向。这种结构的优点是在外延区域形成的器件由氧化物或氮化物相互隔离。

上一篇:向相关的晶圆生长问题是图形偏移

上一篇:多晶硅和非晶硅淀积

热门点击

热门点击

- 芯片和晶圆尺寸的增大

- 双大马士革铜工艺

- 电缆各支持点间的距离

- PE线的重复接地可以降低当相线碰壳短路时的设

- 四探针测试仪测量厚度

- 电压损失是指线路始端电压与末端电压的代数差

- TT系统内的漏电保护器

- 硅湿法刻蚀

- TN-C方式供电系统是用工作零线兼作接零保护

- 退火和杂质激活

推荐技术资料

推荐技术资料

- 硬盘式MP3播放器终级改

- 一次偶然的机会我结识了NE0 2511,那是一个远方的... [详细]

公网安备44030402000607

公网安备44030402000607