TEFGP1C105M8R�����Ŀ�ķ�����֤

����ʱ��:2019/10/26 12:06:21 ���ʴ���:593

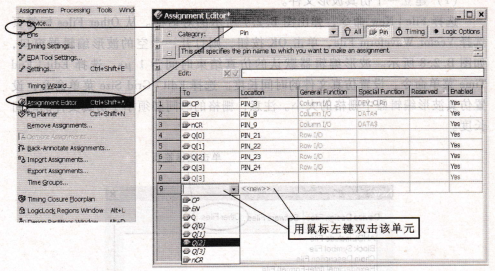

TEFGP1C105M8RAssignment Editor���ŷ������

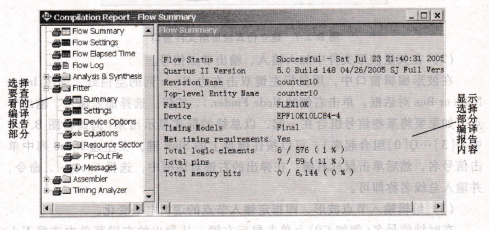

�̵Ľ����Լ�������ʱ��;��Ϣ���ڽ���ʾ��������е���Ϣ�Լ�����г���

�Ĵ���ȡ�����ʱ�����Զ�����ͼb.2.6��ʾ�ı��뱨�洰�ڣ�����ߴ���ѡ��Ҫ�鿴�IJ��֣��������ݻ����ұߴ�����ʾ������

�����Ŀ�ķ�����֤

�ڷ���ǰ,������������ṩ���˼����źš�Quartus ��֧�ֶ�����ʽ��

�����źŸ�ʽ:ʸ�������ļ�(.vwf)��ʸ��������ļ�(.tbl)��,������ֱ��

��TCL����̨�������˼����źš����沽������:

����ʹ�ܿ��ƶ˵�8��һ3�����ȱ���õ�·����Ϊ��������

1·һ4·���ݷ�������·�Ĺ��ܱ������4.6.8��ʾ,INΪ1·����������s0Ϊѡ���ź�,ENΪоƬ��ʹ���ź�,Y3~Y0Ϊ����źš�xΪ����ֵ,zΪҪ��:

��������Ƹõ�·,д����ƹ���,������ͼ���â�ehl��g HDL����Ϊ��ģ��ʽ�����õ�·��

���������ϵͳ��,������Ҫ������������������㹦�ܵ��������·��,����Ҫ���д洢���ܵĵ�·,��ϵ�·��洢��·���Ͽɹ���ʱ������·,���ʱ���·�����½�����ʵ�ִ洢���ܵ���������Ԫ��·,���������ʹ������١������������ǵĵ�·�ṹ�빤��ԭ��,�Լ���ʵ�ֵIJ�ͬ�����ܡ�����,���»��������â�erilog HDL�����������봥�����ķ�����

�������ʹ������ֱ�ϵlatch��nip flop����ơ�

Ϊ�˽���˫��̬�ĸ���,����ͼ5.1.1��ʾ������ģ��������ģ�⡣ģ�͵�����Ϊһ���������һС���λ������ʾ������̬(0,1)��һ�ֽ���̬��(�嶥)����С��ԭ������ߵ���̬,�����������ʩ�ӳ����,����Խ���嶥�Ľ���̬�������ұߵ���һ��̬����֮,��ʱ����С����Ҳ�ʩ��һ����ij����,С���ֽ��ظ���ԭ������̬����Ȼ,ÿ��Ҫ�ı�С��״̬ʱ,��ʩ�ӵij���������㹻��,����С����Խ������̬��λ��,�ֻ᷵�ص�ԭ��״̬��������һ��ģ�Ϳ��������ģ��˫��̬�����������ȶ�״̬��ı仯��

˫��̬�洢��Ԫ��·

��·�ṹ,����������G1��G2�ӳ�ͼ5.1.2��ʾ�Ľ��������ʽ,���������˫��̬��·�����潫������ģ�������Ƕȶ������Ժ���Ϊ���з�����

��״̬����,�ӵ�·������ϵ��֪,��o=0,���ڷ���G2������,��ʹu=1,�����ȡ�һ��ϵ��metastable�����

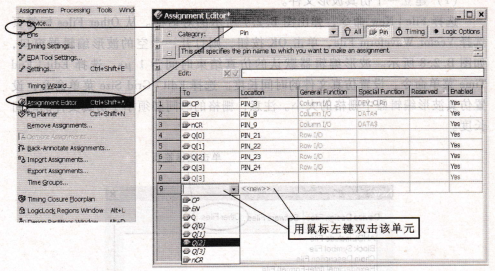

TEFGP1C105M8RAssignment Editor���ŷ������

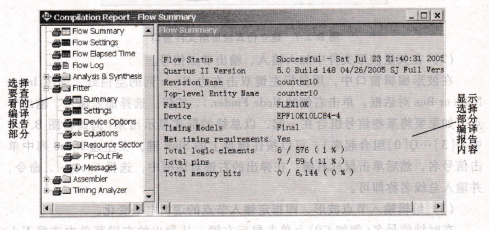

�̵Ľ����Լ�������ʱ��;��Ϣ���ڽ���ʾ��������е���Ϣ�Լ�����г���

�Ĵ���ȡ�����ʱ�����Զ�����ͼb.2.6��ʾ�ı��뱨�洰�ڣ�����ߴ���ѡ��Ҫ�鿴�IJ��֣��������ݻ����ұߴ�����ʾ������

�����Ŀ�ķ�����֤

�ڷ���ǰ,������������ṩ���˼����źš�Quartus ��֧�ֶ�����ʽ��

�����źŸ�ʽ:ʸ�������ļ�(.vwf)��ʸ��������ļ�(.tbl)��,������ֱ��

��TCL����̨�������˼����źš����沽������:

����ʹ�ܿ��ƶ˵�8��һ3�����ȱ���õ�·����Ϊ��������

1·һ4·���ݷ�������·�Ĺ��ܱ������4.6.8��ʾ,INΪ1·����������s0Ϊѡ���ź�,ENΪоƬ��ʹ���ź�,Y3~Y0Ϊ����źš�xΪ����ֵ,zΪҪ��:

��������Ƹõ�·,д����ƹ���,������ͼ���â�ehl��g HDL����Ϊ��ģ��ʽ�����õ�·��

���������ϵͳ��,������Ҫ������������������㹦�ܵ��������·��,����Ҫ���д洢���ܵĵ�·,��ϵ�·��洢��·���Ͽɹ���ʱ������·,���ʱ���·�����½�����ʵ�ִ洢���ܵ���������Ԫ��·,���������ʹ������١������������ǵĵ�·�ṹ�빤��ԭ��,�Լ���ʵ�ֵIJ�ͬ�����ܡ�����,���»��������â�erilog HDL�����������봥�����ķ�����

�������ʹ������ֱ�ϵlatch��nip flop����ơ�

Ϊ�˽���˫��̬�ĸ���,����ͼ5.1.1��ʾ������ģ��������ģ�⡣ģ�͵�����Ϊһ���������һС���λ������ʾ������̬(0,1)��һ�ֽ���̬��(�嶥)����С��ԭ������ߵ���̬,�����������ʩ�ӳ����,����Խ���嶥�Ľ���̬�������ұߵ���һ��̬����֮,��ʱ����С����Ҳ�ʩ��һ����ij����,С���ֽ��ظ���ԭ������̬����Ȼ,ÿ��Ҫ�ı�С��״̬ʱ,��ʩ�ӵij���������㹻��,����С����Խ������̬��λ��,�ֻ᷵�ص�ԭ��״̬��������һ��ģ�Ϳ��������ģ��˫��̬�����������ȶ�״̬��ı仯��

˫��̬�洢��Ԫ��·

��·�ṹ,����������G1��G2�ӳ�ͼ5.1.2��ʾ�Ľ��������ʽ,���������˫��̬��·�����潫������ģ�������Ƕȶ������Ժ���Ϊ���з�����

��״̬����,�ӵ�·������ϵ��֪,��o=0,���ڷ���G2������,��ʹu=1,�����ȡ�һ��ϵ��metastable�����

��һƪ��TLE4271-2���ŷ���

��һƪ��T495V107M010AS ���α༭��

�������

�������

- ConFlow Power��ʽ�Ƴ���һ���ͳ�

- MNBZ5233BLT1�ż�֮������ߵķֲ�

- ��������������Ʒ�����ϵĴ�Ļ��ʽ������

- ATF-55143-TR1 ��·����������ð

- ISL98003CNZ-165 ���ɵ�·����

- 219244-3�������ԷŴ���

- 3NA3354-6�̵�����Ȧ��������������

- LT1328BCS8�û���Ź��ɻ���

- KMPC8264AZUQJDB

- LM25088MH-1 ��������Ĥ������

�Ƽ���������

�Ƽ���������

- Ƶ���ǵĽ������

- �ִ�Ƶ�����ڸ���Դģʽ��Ҳ����ʹ��Maker�͡�Mak... [��ϸ]

��������44030402000607

��������44030402000607