VI-231-EV 石英晶体的电路符号

发布时间:2019/10/24 8:48:20 访问次数:511

VI-231-EV例8.3.1 在图8.3.4中R=10 kΩ,C=0.022 uF,CMOs施密特触发器的yDD F5 V,y。H≈5V,y。L=0Ⅴ,%+=2・75v,%~=1.67Ⅴ,试计算输出波形的高电平持续时间JpH′低电平持续时间JPL和占空比g。

解:电路的输出波形如图8,3,5所示。tPH、JPL实际上就是图8.3.5中的T1和r2,由式(8.3.6)和式(8.3.7)可分别求出

tph=t2=0.439=43,9%

gtph=10t1・0.022*62+110

石英晶体振荡器,用门电路组成的多谐振荡器的振荡周期不仅与时间常数RC有关,而且还取决于门电路的阈值电压%Ⅱ。由于‰Ⅱ容易受温度、电源电压及干扰的影响,因此频率稳定性较差,只能应用于对频率稳定性要求不高的场合。

如果要求产生频率稳定性很高的脉冲波形,就要采用由石英晶体组成的石英晶体振荡器。石英晶体的电路符号和阻抗频率特性如图8.3.6(a)、(b)所示。石英晶体的选频特性非常好,它有一个极为稳定的串联谐振频率及,且等效品质因数Q值也很高。只有频率为入的信号最容易通过,而其他频率的信脉冲波形的变换与产生.

一般模式的读写操作 (b)丛发模式的读写操作

注:图中假设输出使能信号0E始终有效(低电平)。②0(A1)表示Al地址单元中的数据被读出,出现在r/o线上。I(A1)则表示向Al地址单元写人的数据出现在〃o线上。实际上,J/o线上的数据是前一个CP沿作用的结果。③A1+1表示在A1地址基础上,由丛发计数器产生的第一个地址,A1+2表示由丛发计数器产生的第二个地址,余类推。

来时,由丛发计数器在上一个A1⒕。基础上,计数生成下一个地址的AIAO进行读/写。由于丛发计数器是2位计数器,所以在ADy保持高电平时,可以连续生成4个不同的地址。sSRAM的这种丛发模式,在连续读/写多个字时.

减少外部地址总线的占用时间,提高读写效率。读/写时,每4个字一组,外部只需提供首地址,其余3个地址由ssRAM内部丛发计数器产生。如果超过4个时钟周期仍保持丛发模式(不读人新的外部地址),则按丛发计数器循环产生的地址进行读/写操作。丛发模式的读写操作过程如图7.2.6(b)所示。

在由sSRAM构成的计算机系统中,由于在时钟有效沿到来时,地址、数据、控制等信号被锁存到ssRAM内部的寄存器中,因此读写过程的延时等待均在时钟作用下由sSRAM内部控制完成。此时,系统中的微处理器在读写sSRAM的同时,可以处理其他任务,从而提高了整个系统的工作速度。另外,由于sSRAM采用与时钟同步的方式工作,因此可以将读写过程的各种延时进行优化设计,且限制在芯片内部,使得sSRAM的读写速度高于SRAM。sSRAM的这种同步工作方式也使其应用更简便。用户使用时,所有的输人信号只要围绕时钟的有效沿进行设计即可。因此,目前ssRAM已广泛应用于各种同步工作的数字系统中,特别是与处理器一同工作的系统,例如个人电脑中的超高速缓冲存储器(Cache)。

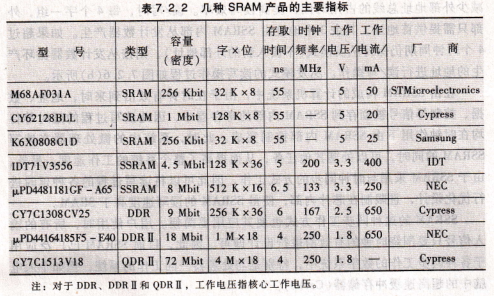

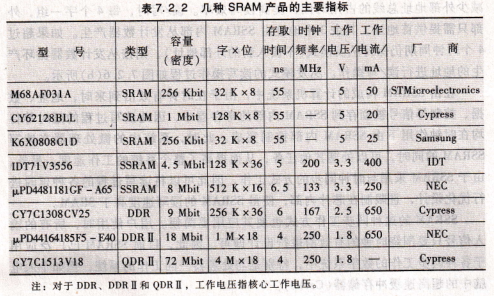

其他SSRAM,随着计算机技术及相关行业(例如互联网)的快速发展,对存储器提出了更高的要求。高速、高密度、低功耗早已成为RAM发展的永恒主题。在ss-RAM之后,各大RAM厂商又先后开发出双倍数据传输率静态随机存取存储器(DDR①SRAM)和四倍数据传输率静态随机存取存储器(QDR②SRAM)。

上述sSRAM只在时钟的上升沿传输数据,并且共用读/写数据总线,读和写只能分时进行。这种sSRAM也称为单倍数据传输率静态随机存取存储器(SDR③SRAM)。DDR SRAM是在ssRAM基础上经过改进,在每个时钟周期的上升沿和下降沿各传输一次数据,这样数据传输效率提高了一倍,但是读写仍不能同时进行。

QDR SRAM进一步改进了结构,为读和写操作分别提供独立的接口,不但在每个时钟周期的上升沿和下降沿共传输两次数据,而且每次读写能够同时进行,避免了数据总线的争抢,使数据传输效率相对于ssRAM提高了两倍。对DDR和QDR某些性能进行改善后的产品称为DDR Ⅱ和QDR Ⅱ SRAM。

目前,采用0.09 um工艺技术生产的SRAM最高容量已达72 Mbit,最高时钟工作频率达到333 MHz。

VI-231-EV例8.3.1 在图8.3.4中R=10 kΩ,C=0.022 uF,CMOs施密特触发器的yDD F5 V,y。H≈5V,y。L=0Ⅴ,%+=2・75v,%~=1.67Ⅴ,试计算输出波形的高电平持续时间JpH′低电平持续时间JPL和占空比g。

解:电路的输出波形如图8,3,5所示。tPH、JPL实际上就是图8.3.5中的T1和r2,由式(8.3.6)和式(8.3.7)可分别求出

tph=t2=0.439=43,9%

gtph=10t1・0.022*62+110

石英晶体振荡器,用门电路组成的多谐振荡器的振荡周期不仅与时间常数RC有关,而且还取决于门电路的阈值电压%Ⅱ。由于‰Ⅱ容易受温度、电源电压及干扰的影响,因此频率稳定性较差,只能应用于对频率稳定性要求不高的场合。

如果要求产生频率稳定性很高的脉冲波形,就要采用由石英晶体组成的石英晶体振荡器。石英晶体的电路符号和阻抗频率特性如图8.3.6(a)、(b)所示。石英晶体的选频特性非常好,它有一个极为稳定的串联谐振频率及,且等效品质因数Q值也很高。只有频率为入的信号最容易通过,而其他频率的信脉冲波形的变换与产生.

一般模式的读写操作 (b)丛发模式的读写操作

注:图中假设输出使能信号0E始终有效(低电平)。②0(A1)表示Al地址单元中的数据被读出,出现在r/o线上。I(A1)则表示向Al地址单元写人的数据出现在〃o线上。实际上,J/o线上的数据是前一个CP沿作用的结果。③A1+1表示在A1地址基础上,由丛发计数器产生的第一个地址,A1+2表示由丛发计数器产生的第二个地址,余类推。

来时,由丛发计数器在上一个A1⒕。基础上,计数生成下一个地址的AIAO进行读/写。由于丛发计数器是2位计数器,所以在ADy保持高电平时,可以连续生成4个不同的地址。sSRAM的这种丛发模式,在连续读/写多个字时.

减少外部地址总线的占用时间,提高读写效率。读/写时,每4个字一组,外部只需提供首地址,其余3个地址由ssRAM内部丛发计数器产生。如果超过4个时钟周期仍保持丛发模式(不读人新的外部地址),则按丛发计数器循环产生的地址进行读/写操作。丛发模式的读写操作过程如图7.2.6(b)所示。

在由sSRAM构成的计算机系统中,由于在时钟有效沿到来时,地址、数据、控制等信号被锁存到ssRAM内部的寄存器中,因此读写过程的延时等待均在时钟作用下由sSRAM内部控制完成。此时,系统中的微处理器在读写sSRAM的同时,可以处理其他任务,从而提高了整个系统的工作速度。另外,由于sSRAM采用与时钟同步的方式工作,因此可以将读写过程的各种延时进行优化设计,且限制在芯片内部,使得sSRAM的读写速度高于SRAM。sSRAM的这种同步工作方式也使其应用更简便。用户使用时,所有的输人信号只要围绕时钟的有效沿进行设计即可。因此,目前ssRAM已广泛应用于各种同步工作的数字系统中,特别是与处理器一同工作的系统,例如个人电脑中的超高速缓冲存储器(Cache)。

其他SSRAM,随着计算机技术及相关行业(例如互联网)的快速发展,对存储器提出了更高的要求。高速、高密度、低功耗早已成为RAM发展的永恒主题。在ss-RAM之后,各大RAM厂商又先后开发出双倍数据传输率静态随机存取存储器(DDR①SRAM)和四倍数据传输率静态随机存取存储器(QDR②SRAM)。

上述sSRAM只在时钟的上升沿传输数据,并且共用读/写数据总线,读和写只能分时进行。这种sSRAM也称为单倍数据传输率静态随机存取存储器(SDR③SRAM)。DDR SRAM是在ssRAM基础上经过改进,在每个时钟周期的上升沿和下降沿各传输一次数据,这样数据传输效率提高了一倍,但是读写仍不能同时进行。

QDR SRAM进一步改进了结构,为读和写操作分别提供独立的接口,不但在每个时钟周期的上升沿和下降沿共传输两次数据,而且每次读写能够同时进行,避免了数据总线的争抢,使数据传输效率相对于ssRAM提高了两倍。对DDR和QDR某些性能进行改善后的产品称为DDR Ⅱ和QDR Ⅱ SRAM。

目前,采用0.09 um工艺技术生产的SRAM最高容量已达72 Mbit,最高时钟工作频率达到333 MHz。

上一篇:TPS842A 振荡周期的计算

公网安备44030402000607

公网安备44030402000607