TSC87C52-16CA反相器间的耦合

发布时间:2019/10/24 8:52:18 访问次数:641

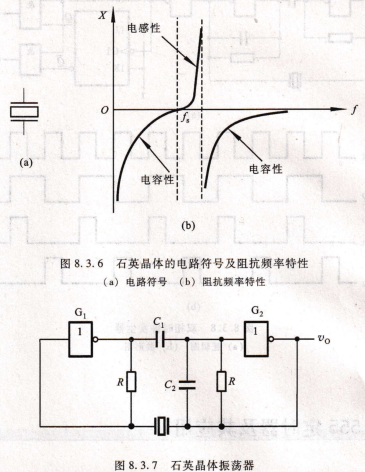

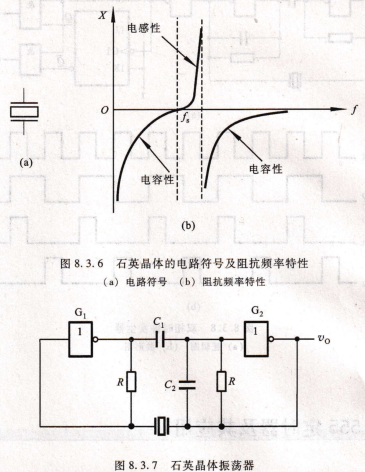

TSC87C52-16CA石英晶体振荡器电路如图8.3.7所示。图中,并联在两个反相器输入、输出间的电阻R的作用是使反相器工作在线性放大区。R的阻值,对于TTL门电路通常在0.7~2 kΩ之间;对于CMOs门则常在10~100 MΩ之间。电路中,电容Ct用于两个反相器间的耦合,而C2的作用,则是抑制高次谐波,以保证稳定的频率输出。电容C2的选择应使2πRC矾≈1,从而使RC2并联网络在益处产生极点,以减少谐振信号损失。C1的选择应使C】在频率为正时的容抗可以忽略不计。电路的振荡频率仅取决于石英晶体的串联谐振频率互,而与电路中的R、C的数值无关。

为了改善输出波形,增强带负载的能力,通常在振荡器的输出端再加一级反相器。作为一个应用实例,双相时钟发生器如图8.3.8(a)所示,其波形如图8.3.8(b)所示。 `

读写控制WE为高电平,输出缓冲器/灵敏放大器被选通,C中存储的数据通过位线和缓冲器输出(D。再经列选通电路送至最终的输出引脚)。由于读出时会消耗C中的电荷,存储的数据被破坏,故每次读出后,必须及时对读出单元刷新,即此时刷新控制R也为高电平,则读出的数据又经刷新缓冲器和位线对电容器C进行刷新。

动态存储单元及基本操作原理

除了读、写操作可以对存储单元进行刷新外,刷新操作也可以通过只选通行选线来实现。例如,当行选线X为高电平,且WE亦为高电平时,C上的数据经T到达位线B,然后经输入缓冲器对存储单元刷新,此时的刷新是整行刷新。实际上,输出缓冲器和刷新缓冲器环路构成一正反馈,如果位线为高电平,则将位线电平拉向更高。反之则使位线电平降得更低。

由于存储单元电容的容量很小,所以在位线容性负载较大时,C中存储的电荷(C存有1时)可能还未将位线拉至高电平时便耗尽了,由此出现读出错误。为避免出现这种情况,通常在读之前先将位线电平预置为高、低电平的中间值。这样,T导通时,根据电容C存储的是0还是1,会将位线拉向低电平或高电平。位线电平的这种变化经灵敏放大器放大,可以准确得到C所存储的逻辑值。

DRAM的基本结构和操作时序,由于DRAM的集成度很高,存储容量大,因此需要较多的地址线。为减少引线数目,DRAM大都采用行、列地址分时送入的方法。例如,对于一个1M字的存储器,有22°个地址,即有20根地址线。采用行、列地址分时送人时,只需要10根地址线。DRAM的基本结构如图7.2.8所示,其内部设有行.

号CAs②控制,送人各自的寄存器。此外,DRAM内部还设有刷新计数器和刷新控制及定时电路,由此可以自动产生行地址进行刷新。

DRAM的操作方式比SRAM要复杂些,这里只举出几种典型操作。

读/写操作时,首先RAs和CAS先后变为低电平,将行和列地址分别送入相应地址寄存器。然后在读写控制信号WE作用下完成读/写操作。读操作时,输出使能0E应为低电平。操作时序如图7.2.9(a)所示。

页模式操作,所谓“页”是指同一行的所有列构成的存储单元。页模式下的读写操作与一般读写操作的差别在于不改变行地址,而只改变列地址。但行地址选择RAS必须始终保持低电平。页模式可以显著提高读写速度,其读操作时序如图7.2.9(b)所示。

RAs只刷新操作,该操作只刷新行地址指定行的所有存储单元,不进行任何实际的读写操作。在整个操作周期CAs要保持高电平,其时序如图7.2.9(c)所示。该操作一次只刷新一行,且需要外部地址计数器提供刷新地址。

系Row Address strobe的缩写。

系Column Address strobe的缩写。

TSC87C52-16CA石英晶体振荡器电路如图8.3.7所示。图中,并联在两个反相器输入、输出间的电阻R的作用是使反相器工作在线性放大区。R的阻值,对于TTL门电路通常在0.7~2 kΩ之间;对于CMOs门则常在10~100 MΩ之间。电路中,电容Ct用于两个反相器间的耦合,而C2的作用,则是抑制高次谐波,以保证稳定的频率输出。电容C2的选择应使2πRC矾≈1,从而使RC2并联网络在益处产生极点,以减少谐振信号损失。C1的选择应使C】在频率为正时的容抗可以忽略不计。电路的振荡频率仅取决于石英晶体的串联谐振频率互,而与电路中的R、C的数值无关。

为了改善输出波形,增强带负载的能力,通常在振荡器的输出端再加一级反相器。作为一个应用实例,双相时钟发生器如图8.3.8(a)所示,其波形如图8.3.8(b)所示。 `

读写控制WE为高电平,输出缓冲器/灵敏放大器被选通,C中存储的数据通过位线和缓冲器输出(D。再经列选通电路送至最终的输出引脚)。由于读出时会消耗C中的电荷,存储的数据被破坏,故每次读出后,必须及时对读出单元刷新,即此时刷新控制R也为高电平,则读出的数据又经刷新缓冲器和位线对电容器C进行刷新。

动态存储单元及基本操作原理

除了读、写操作可以对存储单元进行刷新外,刷新操作也可以通过只选通行选线来实现。例如,当行选线X为高电平,且WE亦为高电平时,C上的数据经T到达位线B,然后经输入缓冲器对存储单元刷新,此时的刷新是整行刷新。实际上,输出缓冲器和刷新缓冲器环路构成一正反馈,如果位线为高电平,则将位线电平拉向更高。反之则使位线电平降得更低。

由于存储单元电容的容量很小,所以在位线容性负载较大时,C中存储的电荷(C存有1时)可能还未将位线拉至高电平时便耗尽了,由此出现读出错误。为避免出现这种情况,通常在读之前先将位线电平预置为高、低电平的中间值。这样,T导通时,根据电容C存储的是0还是1,会将位线拉向低电平或高电平。位线电平的这种变化经灵敏放大器放大,可以准确得到C所存储的逻辑值。

DRAM的基本结构和操作时序,由于DRAM的集成度很高,存储容量大,因此需要较多的地址线。为减少引线数目,DRAM大都采用行、列地址分时送入的方法。例如,对于一个1M字的存储器,有22°个地址,即有20根地址线。采用行、列地址分时送人时,只需要10根地址线。DRAM的基本结构如图7.2.8所示,其内部设有行.

号CAs②控制,送人各自的寄存器。此外,DRAM内部还设有刷新计数器和刷新控制及定时电路,由此可以自动产生行地址进行刷新。

DRAM的操作方式比SRAM要复杂些,这里只举出几种典型操作。

读/写操作时,首先RAs和CAS先后变为低电平,将行和列地址分别送入相应地址寄存器。然后在读写控制信号WE作用下完成读/写操作。读操作时,输出使能0E应为低电平。操作时序如图7.2.9(a)所示。

页模式操作,所谓“页”是指同一行的所有列构成的存储单元。页模式下的读写操作与一般读写操作的差别在于不改变行地址,而只改变列地址。但行地址选择RAS必须始终保持低电平。页模式可以显著提高读写速度,其读操作时序如图7.2.9(b)所示。

RAs只刷新操作,该操作只刷新行地址指定行的所有存储单元,不进行任何实际的读写操作。在整个操作周期CAs要保持高电平,其时序如图7.2.9(c)所示。该操作一次只刷新一行,且需要外部地址计数器提供刷新地址。

系Row Address strobe的缩写。

系Column Address strobe的缩写。

公网安备44030402000607

公网安备44030402000607