TPS842A 振荡周期的计算

发布时间:2019/10/24 8:43:05 访问次数:739

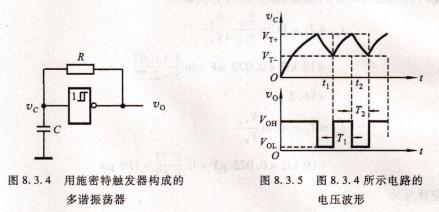

TPS842A由于施密特触发器有vt+和vt-两个不同的阈值电压,如果能使其输人电压能在vt+和vt-之间不停地反复变化,就可以在它的输出端得到矩形波。实现上述设想的一种简单方法就是,将施密特触发器的输出端经RC积分电路接回其输入端即可,电路如图8,3.4所示。

工作原理,设接通电源瞬间,电容器C上的初始电压为零,输出电压vo为高电平。

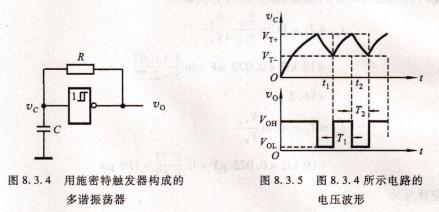

u0通过电阻R对电容器C充电,当vc达到%+时,施密特触发器翻转,u0跳变为低电平。此后,电容器C又开始放电,vc下降,当它下降到%~时,电路又发生翻转,u0又由低电平跳变为高电平,C又被重新充电。如此周而复始,在电路的输出端,就得到了矩形波。uc和v0的波形如图8.3.5所示。

振荡周期的计算,设在图8.3.4中采用CMOs施密特触发器CC40106,已知v0h≈vDD、voL≈OV,则图8,3,5中的输出电压v0的周期T=r1+%,计算如下:

t1的计算,以图8.3.5中J1作为时间起点,根据RC电路暂态过渡过程公式则有vI(0十)=%~,v1(∞)=/DD,vI(r1)=%+,t=RC

于是可求出

rRcln11vdd-vt/vdd-vt+ (8.3.5)

t2的计算

以图8.3.5中艺2作为时间起点,则有读操作时,控制信号和地址输人在CP的上升沿被取样,当丛发使能控制ADy和片选CE为低电平时,地址线上的地址被锁存到地址寄存器中,高电平的WE也被寄存到读写控制逻辑电路中。此时,读写控制逻辑电路使数据选择器选择地址寄存器中的地址进行译码,在下一个CP有效沿到来前,存储阵列中的数据被送到数据线f/o上输出。

写操作与读操作类似,只是被取样的WE为低电平。而输人的数据在接下来的CP上升沿锁存到输人寄存器中,同时地址寄存器中的地址又传至写地址寄存器中。此时,读写控制逻辑电路使数据选择器选择写地址寄存器中的地址进行译码,在输入驱动电路的作用下,将输人寄存器中的数据写人存储阵列。写操作时,读写控制逻辑电路将自动屏蔽输出使能信号oE,使三态输出缓冲器呈现高阻态。

丛发模式读写操作是sSRAM中特有的①。当丛发使能控制且D/为低电平时,A1A。可直接穿过丛发控制逻辑电路,按外部给定的地址进行读/写,此时就是上述的一般读写操作。但当丛发使能控制ADy为高电平时,地址寄存器不接收外部新地址而保持上一个时钟周期输人的地址,在CP下一个上升沿到不仅SSRAM中有丛发模式,而且sDRAM中也有该模式.

TPS842A由于施密特触发器有vt+和vt-两个不同的阈值电压,如果能使其输人电压能在vt+和vt-之间不停地反复变化,就可以在它的输出端得到矩形波。实现上述设想的一种简单方法就是,将施密特触发器的输出端经RC积分电路接回其输入端即可,电路如图8,3.4所示。

工作原理,设接通电源瞬间,电容器C上的初始电压为零,输出电压vo为高电平。

u0通过电阻R对电容器C充电,当vc达到%+时,施密特触发器翻转,u0跳变为低电平。此后,电容器C又开始放电,vc下降,当它下降到%~时,电路又发生翻转,u0又由低电平跳变为高电平,C又被重新充电。如此周而复始,在电路的输出端,就得到了矩形波。uc和v0的波形如图8.3.5所示。

振荡周期的计算,设在图8.3.4中采用CMOs施密特触发器CC40106,已知v0h≈vDD、voL≈OV,则图8,3,5中的输出电压v0的周期T=r1+%,计算如下:

t1的计算,以图8.3.5中J1作为时间起点,根据RC电路暂态过渡过程公式则有vI(0十)=%~,v1(∞)=/DD,vI(r1)=%+,t=RC

于是可求出

rRcln11vdd-vt/vdd-vt+ (8.3.5)

t2的计算

以图8.3.5中艺2作为时间起点,则有读操作时,控制信号和地址输人在CP的上升沿被取样,当丛发使能控制ADy和片选CE为低电平时,地址线上的地址被锁存到地址寄存器中,高电平的WE也被寄存到读写控制逻辑电路中。此时,读写控制逻辑电路使数据选择器选择地址寄存器中的地址进行译码,在下一个CP有效沿到来前,存储阵列中的数据被送到数据线f/o上输出。

写操作与读操作类似,只是被取样的WE为低电平。而输人的数据在接下来的CP上升沿锁存到输人寄存器中,同时地址寄存器中的地址又传至写地址寄存器中。此时,读写控制逻辑电路使数据选择器选择写地址寄存器中的地址进行译码,在输入驱动电路的作用下,将输人寄存器中的数据写人存储阵列。写操作时,读写控制逻辑电路将自动屏蔽输出使能信号oE,使三态输出缓冲器呈现高阻态。

丛发模式读写操作是sSRAM中特有的①。当丛发使能控制且D/为低电平时,A1A。可直接穿过丛发控制逻辑电路,按外部给定的地址进行读/写,此时就是上述的一般读写操作。但当丛发使能控制ADy为高电平时,地址寄存器不接收外部新地址而保持上一个时钟周期输人的地址,在CP下一个上升沿到不仅SSRAM中有丛发模式,而且sDRAM中也有该模式.

公网安备44030402000607

公网安备44030402000607