XRCGB32M000F2P消去竞争冒险的方法

发布时间:2019/10/12 21:46:50 访问次数:2248

XRCGB32M000F2P综上所述,当一个逻辑门的两个输入端的信号同时向相反方向变化,而变化的时间有差异的现象,称为竞争。两个输入端可以是不同变量所产生的信号,但其取值的变化方向是相反的,如图4.3.1和如图4.3.2中的AB及A+B.也可以是在一定条件下,门电路输出端的逻辑表达式简化成两个互补信号相乘或者相加,即L=A・A或者L=A+A,如图4.3.3所示。由竞争而可能产生输出干扰脉冲的现象称为冒险。

在考虑延迟的条件下,若与门的两个输人A和A,其中―个先从0变1时,则A・A会向其非稳定值1变化,此时会产生冒险;若或门的两个输入且和A,其中一个先从1变0时,则A+A会向其非稳定值0变化,也会产生冒险。两者之间存在对偶关系。

值得注意的是,有竞争现象时不一定都会产生干扰脉冲,如图4.3.1(a)所示,如果A从0变为1时刻没有滞后信号B的变化,则输出不会产生冒险。在一个复杂的逻辑系统中,由于信号的传输路径不同,或者各个信号延迟时间的差异、信号变化的互补性以及其他一些因素,很容易产生竞争冒险现象。因此在电路设计中应尽量减小冒险产生。

消去竞争冒险的方法

针对上述原因,可以采取以下措施来消去竞争冒险现象。

发现并消去互补相乘项

例如,函数式F=(处+B)(A+C),在B=C=0时,F=AA。若直接根据这个逻辑表达式组成逻辑电路,则可能出现竞争冒险。如将该式变换为F=

AA+AC+AB+BC=AC+AB+BC,这里已将AA消掉。根据这个表达式组成逻辑电路就不会出现竞争冒险。

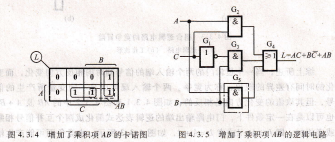

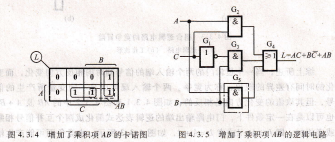

增加乘积项以避免互补项相加,对于图4.3.3(a)所示的逻辑电路,可以根据常用恒等式增加乘积项,将输出逻辑表达式L=AC+BC变为L=AC+BC+AB,如图4.3.4卡诺图所示。对应的逻辑电路如图4.3.5示。当A=B=1时,根据逻辑表达式有L=C+C+1,不会只出现互补项相加的情况,而此时电路中,G5输出为1,使G4输出亦为1,这就消除了C的状态变化对输出状态的影响,从而消去了竞争冒险。

XRCGB32M000F2P综上所述,当一个逻辑门的两个输入端的信号同时向相反方向变化,而变化的时间有差异的现象,称为竞争。两个输入端可以是不同变量所产生的信号,但其取值的变化方向是相反的,如图4.3.1和如图4.3.2中的AB及A+B.也可以是在一定条件下,门电路输出端的逻辑表达式简化成两个互补信号相乘或者相加,即L=A・A或者L=A+A,如图4.3.3所示。由竞争而可能产生输出干扰脉冲的现象称为冒险。

在考虑延迟的条件下,若与门的两个输人A和A,其中―个先从0变1时,则A・A会向其非稳定值1变化,此时会产生冒险;若或门的两个输入且和A,其中一个先从1变0时,则A+A会向其非稳定值0变化,也会产生冒险。两者之间存在对偶关系。

值得注意的是,有竞争现象时不一定都会产生干扰脉冲,如图4.3.1(a)所示,如果A从0变为1时刻没有滞后信号B的变化,则输出不会产生冒险。在一个复杂的逻辑系统中,由于信号的传输路径不同,或者各个信号延迟时间的差异、信号变化的互补性以及其他一些因素,很容易产生竞争冒险现象。因此在电路设计中应尽量减小冒险产生。

消去竞争冒险的方法

针对上述原因,可以采取以下措施来消去竞争冒险现象。

发现并消去互补相乘项

例如,函数式F=(处+B)(A+C),在B=C=0时,F=AA。若直接根据这个逻辑表达式组成逻辑电路,则可能出现竞争冒险。如将该式变换为F=

AA+AC+AB+BC=AC+AB+BC,这里已将AA消掉。根据这个表达式组成逻辑电路就不会出现竞争冒险。

增加乘积项以避免互补项相加,对于图4.3.3(a)所示的逻辑电路,可以根据常用恒等式增加乘积项,将输出逻辑表达式L=AC+BC变为L=AC+BC+AB,如图4.3.4卡诺图所示。对应的逻辑电路如图4.3.5示。当A=B=1时,根据逻辑表达式有L=C+C+1,不会只出现互补项相加的情况,而此时电路中,G5输出为1,使G4输出亦为1,这就消除了C的状态变化对输出状态的影响,从而消去了竞争冒险。

公网安备44030402000607

公网安备44030402000607