源极跟随器十恒流负载

发布时间:2012/8/17 20:29:30 访问次数:1962

图4.17的电路中将源极跟随器的TC4066BP源极电阻置换成了恒流电路(叫做恒流负载)。

图4.1所示的电路中,使用电阻负载(R。)的源极跟随器像照片4.7那样受到空载电流的制约,当负载重时输出波形的负半周被限幅。如图4.6所示,认为这个限幅的电压值就是源极电阻与负载并联接续时的电压降。

图4.17的电路在源极采用了恒流电路,所以可以认为源极电阻是无穷大(恒流电路的阻抗为无穷大),因此源极电阻与负载的并联值就是负载值。就是说,如果空载电流是相同的,那么恒流负载源极跟随器的输出电压可以大于电阻负载源极跟随器的输出电压。

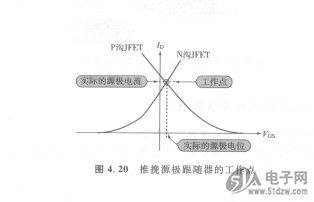

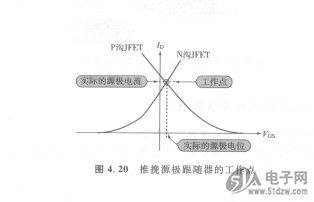

在设计电阻负载源极跟随器时,是从FET的传输特性中求得VGS,计算源极电阻。但是在图4.17的电路中,恒流负载是利用JFET的IDSS的恒流电路,所以确定源极电流的设定值时,只要选择其IDSS与设定的恒流电路的源极电流相等的JFET就可似了。

因此,即使不知道这个电路中Tr.的VG。值也能够进行设计。但是必须确认VGS为多大时才能够工作。图4.17的电路中,根据Tr.、Tr2的IDSS的分散性,取值范围应该为-1~-0.1V(根据2SK371BL,V的传输特性)。

在设计上应该注意的是对于Tr。的FET来说,要选择其IDSS比Tri小的型号或者IDSS档次。其目的是源极跟随器工作时JFET的源极电流设定值低于IDSS。

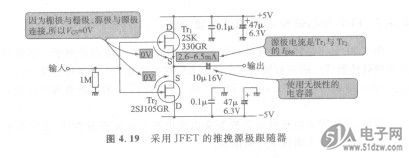

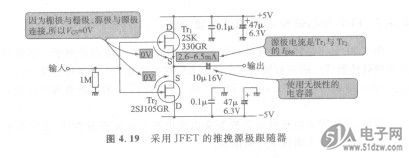

在这个电路中,Tr.采用IDss一8~30mA的2SK371BL,V(东芝),Trz采用IDSS=2.6~6.5mA的2SK330GR。

Tri的栅极偏置电路采用正负二电源(±5V),将栅极电位设定为OV(GND电平),所以只需要一个lMfl的电阻。

如果恒流电路使用JFET,由于源极电流的设定值就是恒流电路中JFET的IDSS,所以分散范围比较大(在图4.17中为2.6~6.5mA)。

如果希望准确地设定源极电流,电路就变得稍微复杂。不过可以使用图4.18所示的晶体管恒流电路。在这种场合由于Tr.也采用JFET,所以恒流电路的设定电流(-Tr1的源极电流)必须设定为低于Tri的IDSS值。

图4.17的电路中将源极跟随器的TC4066BP源极电阻置换成了恒流电路(叫做恒流负载)。

图4.1所示的电路中,使用电阻负载(R。)的源极跟随器像照片4.7那样受到空载电流的制约,当负载重时输出波形的负半周被限幅。如图4.6所示,认为这个限幅的电压值就是源极电阻与负载并联接续时的电压降。

图4.17的电路在源极采用了恒流电路,所以可以认为源极电阻是无穷大(恒流电路的阻抗为无穷大),因此源极电阻与负载的并联值就是负载值。就是说,如果空载电流是相同的,那么恒流负载源极跟随器的输出电压可以大于电阻负载源极跟随器的输出电压。

在设计电阻负载源极跟随器时,是从FET的传输特性中求得VGS,计算源极电阻。但是在图4.17的电路中,恒流负载是利用JFET的IDSS的恒流电路,所以确定源极电流的设定值时,只要选择其IDSS与设定的恒流电路的源极电流相等的JFET就可似了。

因此,即使不知道这个电路中Tr.的VG。值也能够进行设计。但是必须确认VGS为多大时才能够工作。图4.17的电路中,根据Tr.、Tr2的IDSS的分散性,取值范围应该为-1~-0.1V(根据2SK371BL,V的传输特性)。

在设计上应该注意的是对于Tr。的FET来说,要选择其IDSS比Tri小的型号或者IDSS档次。其目的是源极跟随器工作时JFET的源极电流设定值低于IDSS。

在这个电路中,Tr.采用IDss一8~30mA的2SK371BL,V(东芝),Trz采用IDSS=2.6~6.5mA的2SK330GR。

Tri的栅极偏置电路采用正负二电源(±5V),将栅极电位设定为OV(GND电平),所以只需要一个lMfl的电阻。

如果恒流电路使用JFET,由于源极电流的设定值就是恒流电路中JFET的IDSS,所以分散范围比较大(在图4.17中为2.6~6.5mA)。

如果希望准确地设定源极电流,电路就变得稍微复杂。不过可以使用图4.18所示的晶体管恒流电路。在这种场合由于Tr.也采用JFET,所以恒流电路的设定电流(-Tr1的源极电流)必须设定为低于Tri的IDSS值。

上一篇:采用N沟JFET和负电源的电路

上一篇: FET与晶体管混合的达林顿连接

公网安备44030402000607

公网安备44030402000607