电流模式逻辑双倍数据速率

发布时间:2020/10/29 13:20:09 访问次数:1691

LVDS输出驱动器拓扑结构所示,电路工作时输出电源会产生固定的直流负载电流。这可以避免输出逻辑状态跃迁时典型CMOS输出驱动器中出现的电流尖峰。电路中的标称源电流/吸电流设为3.5 mA,使得端接电阻100 Ω时典型输出电压摆幅为350 mV。电路的共模电平通常设为1.2 V,兼容3.3 V、2.5V和1.8 V电源电压。

有两种书面标准可用来定义LVDS接口。最常用的标准是ANSI/TIA/EIA-644规格,另一种是IEEE标准1596.3.

LVDS需要特别注意信号路由的物理布局,但在采样速率达到200 MSPS或更高时可以为转换器提供许多优势。LVDS的恒定电流使得可以支持许多输出,无需CMOS要求的大量电流吸取。

LVDS还能以双倍数据速率(DDR)模式工作,其中两个数据位可以通过同一个LVDS输出驱动器。

与CMOS相比,可以减少一半的引脚数。还降低了等量数据输出的功耗。对转换器数据输出而言,LVDS确实相比CMOS具有诸多优势,但也和CMOS一样存在一些限制。随着转换器分辨率的增加,LVDS接口所需的数据输出量会变得更难针对PCB布局进行管理。转换器的采样率最终会使接口所需的数据速率超出LVDS的能力。

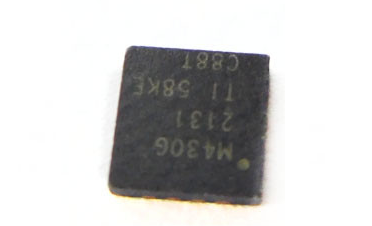

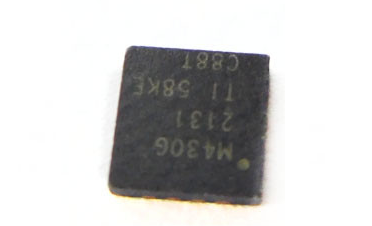

CML输出驱动器转换器数字输出接口的最新趋势是使用具有电流模式逻辑(CML)输出驱动器的串行接口。通常,高分辨率(≥14位)、高速(≥200 Msps)和需要小型封装与低功耗的转换器会使用这些类型的驱动器。CML输出驱动器用在JESD204接口,这种接口目前用于最新转换器。采用具有JESD204接口的CML驱动器后,转换器输出端的数据速率可达12 Gbps(当前版本JESD204B规格)。

需要的输出引脚数也会大幅减少。时钟内置于8b/10b编码数据流,因此无需传输独立时钟信号。数据输出引脚数量也得以减少,最少只需两个。随着转换器的分辨率、速度和通道数的增加,数据输出引脚数可能会相应调整,以满足所需的更高吞吐量。

在采用JESD204接口的CML中,还必须注意数字输出之间的路由路径。需要管理的数据输出大大减少,因此,这一任务比较容易完成,但也不能完全忽略。这种情况下,由于时钟内置于数据中,因此无需担心数据输出和时钟输出之间的时序偏斜。但是,必须注意,接收器中要有合适的时钟和数据恢复(CDR)电路。

除了偏斜之外,还必须关注CMOS和LVDS的建立和保持时间。数据输出必须在时钟边沿跃迁之前的充足时间内驱动到适当的逻辑状态,并且必须在时钟边沿跃迁之后以这种逻辑状态维持充足时间。这可能会受到数据输出和时钟输出之间偏斜的影响,因此,保持良好的时序关系非常重要。由于具有较低信号摆幅和差分信号,LVDS相比CMOS具有一定优势。和CMOS驱动器一样切换逻辑状态时,LVDS输出驱动器无需将这样的大信号驱动至各种不同输出,也不会从电源吸取大量电流。

(素材来源:eccn和21ic和ttic.如涉版权请联系删除。特别感谢)

LVDS输出驱动器拓扑结构所示,电路工作时输出电源会产生固定的直流负载电流。这可以避免输出逻辑状态跃迁时典型CMOS输出驱动器中出现的电流尖峰。电路中的标称源电流/吸电流设为3.5 mA,使得端接电阻100 Ω时典型输出电压摆幅为350 mV。电路的共模电平通常设为1.2 V,兼容3.3 V、2.5V和1.8 V电源电压。

有两种书面标准可用来定义LVDS接口。最常用的标准是ANSI/TIA/EIA-644规格,另一种是IEEE标准1596.3.

LVDS需要特别注意信号路由的物理布局,但在采样速率达到200 MSPS或更高时可以为转换器提供许多优势。LVDS的恒定电流使得可以支持许多输出,无需CMOS要求的大量电流吸取。

LVDS还能以双倍数据速率(DDR)模式工作,其中两个数据位可以通过同一个LVDS输出驱动器。

与CMOS相比,可以减少一半的引脚数。还降低了等量数据输出的功耗。对转换器数据输出而言,LVDS确实相比CMOS具有诸多优势,但也和CMOS一样存在一些限制。随着转换器分辨率的增加,LVDS接口所需的数据输出量会变得更难针对PCB布局进行管理。转换器的采样率最终会使接口所需的数据速率超出LVDS的能力。

CML输出驱动器转换器数字输出接口的最新趋势是使用具有电流模式逻辑(CML)输出驱动器的串行接口。通常,高分辨率(≥14位)、高速(≥200 Msps)和需要小型封装与低功耗的转换器会使用这些类型的驱动器。CML输出驱动器用在JESD204接口,这种接口目前用于最新转换器。采用具有JESD204接口的CML驱动器后,转换器输出端的数据速率可达12 Gbps(当前版本JESD204B规格)。

需要的输出引脚数也会大幅减少。时钟内置于8b/10b编码数据流,因此无需传输独立时钟信号。数据输出引脚数量也得以减少,最少只需两个。随着转换器的分辨率、速度和通道数的增加,数据输出引脚数可能会相应调整,以满足所需的更高吞吐量。

在采用JESD204接口的CML中,还必须注意数字输出之间的路由路径。需要管理的数据输出大大减少,因此,这一任务比较容易完成,但也不能完全忽略。这种情况下,由于时钟内置于数据中,因此无需担心数据输出和时钟输出之间的时序偏斜。但是,必须注意,接收器中要有合适的时钟和数据恢复(CDR)电路。

除了偏斜之外,还必须关注CMOS和LVDS的建立和保持时间。数据输出必须在时钟边沿跃迁之前的充足时间内驱动到适当的逻辑状态,并且必须在时钟边沿跃迁之后以这种逻辑状态维持充足时间。这可能会受到数据输出和时钟输出之间偏斜的影响,因此,保持良好的时序关系非常重要。由于具有较低信号摆幅和差分信号,LVDS相比CMOS具有一定优势。和CMOS驱动器一样切换逻辑状态时,LVDS输出驱动器无需将这样的大信号驱动至各种不同输出,也不会从电源吸取大量电流。

(素材来源:eccn和21ic和ttic.如涉版权请联系删除。特别感谢)

上一篇:正温度系数热敏电阻的检测

公网安备44030402000607

公网安备44030402000607