XC3064L-8TQG144I 绝缘胶带和热缩套管

发布时间:2020/1/7 21:57:33 访问次数:1087

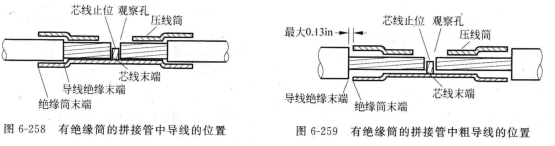

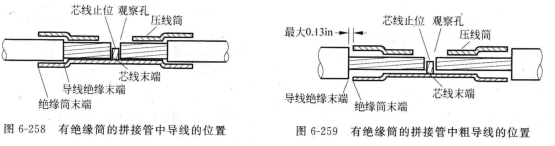

XC3064L-8TQG144I将去除绝缘层的导线放人拼接管,检查导线在拼接管内的位置,如图6-258和图6-259所示。

拼接管压接完成后,在拼接管上缠绕两层绝缘胶带,第一层绝缘胶带紧紧地缠绕在拼接管上,确保胶带末端大于拼接管两侧末端最少0.6~0.85in,胶带缠绕时最小重叠50%;第一层绝缘胶带缠绕后,再逆时针紧紧地缠绕第二层绝缘胶带,第一层胶带的终点就是第二层的起点,第二层的终点就是第一层起点,胶带缠绕时最小重叠50%。

选择合适温度等级的绝缘胶带和热缩套管,确保合金拼接管的最大直径在热缩套管的收缩范围之内。截取合适的热缩套管长度,热缩套管伸出拼接管末端最少1.1in。将防护完成的拼接管放置在热缩套管中心,使用热缩工具完成热缩工作。

拼接管在标准线路施工手册的查找,在维护检查工作中发现一架波音B737-800飞机驾驶舱P6板上有一根导线出现严重损坏,这根导线连接C786跳开关的=L终端到插座D4082oJ的6号孔位,导线长度可以再做一次永久修理,导线标识是o224-24;由于这根导线位于驾驶舱,可千差万别,但它们仍有共同之处,是一般CPLD器件的结构框图。其中逻辑块①就相当于一个GAL器件(见6,7节),CPLD中有多个逻辑块,这些逻辑块之间可以使用可编程内部连线实现相互连接。为了增强对I/0的控制能力,提高引脚的适应性,CPLD中还增加了I/o控制块。每个I/0块中有若干个I/o单元。

可编程乘积项阵,乘积项阵列有汜个输入,可以产生而变量的乘积项。一般一个宏单元对应5个乘积项,这样,在逻辑块中共有5×屁个乘积项。例如,XC9500系列的逻辑块中有90个36变量乘积项,MAX7000系列的逻辑块中有80个36变量乘积项。

乘积项分配和宏单元,不同型号的CPLD器件,乘积项分配和宏单元电路结构也不完全相同,但所要实现的功能大体相似。为XC9500系列的乘积项分配和宏单元电路。图中S1~S:为可编程数据分配器,M1~M5为可编程数据选择器。为简明起见,没有画出它们的可编程选择输入端。

或下一个宏单元去。这种乘积项的“链式”结构,可以实现远远多于5个乘积项的与一或式。在XC9500系列CPLD中,理论上可以将90个乘积项组合到一个宏单元中,产生90个乘积项的与一或式,但此时其余17个宏单元将不能使用乘积项了。在Altera公司生产的CPLD中,宏单元中除了有乘积项扩展功能外,还有乘积项共享电路,使得同一个乘积项可以被多个宏单元同时使用。

数据分配器S1~S5中间输出的乘积项用于特殊功能,这些功能包括作为触发器FF的置位、复位、时钟信号,异或门G5的同相/反相输出控制信号和乘积项输出使能控制信号PrOE。

或门G4输出的与一或式送至异或门G5,G5的另一输入来自数据选择器M1。通过对M1的编程,可以选择0、1或另一个乘积项,来控制G4的输出经G5是否反相,或受另一个乘积项控制。M3可以选择是直接组合形式输出还是经过触发器的寄存器形式输出,触发器FF可以被编程为D触发器或r触发器,且通过M2和M5可以选择全局或乘积项置位、复位信号。通过M4也可以在3个全局时钟和一个乘积项中选择触发器的时钟信号。

宏单元的输出不仅送至I/0单元,还送到内部可编程连线区,以被其他宏单元使用。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

XC3064L-8TQG144I将去除绝缘层的导线放人拼接管,检查导线在拼接管内的位置,如图6-258和图6-259所示。

拼接管压接完成后,在拼接管上缠绕两层绝缘胶带,第一层绝缘胶带紧紧地缠绕在拼接管上,确保胶带末端大于拼接管两侧末端最少0.6~0.85in,胶带缠绕时最小重叠50%;第一层绝缘胶带缠绕后,再逆时针紧紧地缠绕第二层绝缘胶带,第一层胶带的终点就是第二层的起点,第二层的终点就是第一层起点,胶带缠绕时最小重叠50%。

选择合适温度等级的绝缘胶带和热缩套管,确保合金拼接管的最大直径在热缩套管的收缩范围之内。截取合适的热缩套管长度,热缩套管伸出拼接管末端最少1.1in。将防护完成的拼接管放置在热缩套管中心,使用热缩工具完成热缩工作。

拼接管在标准线路施工手册的查找,在维护检查工作中发现一架波音B737-800飞机驾驶舱P6板上有一根导线出现严重损坏,这根导线连接C786跳开关的=L终端到插座D4082oJ的6号孔位,导线长度可以再做一次永久修理,导线标识是o224-24;由于这根导线位于驾驶舱,可千差万别,但它们仍有共同之处,是一般CPLD器件的结构框图。其中逻辑块①就相当于一个GAL器件(见6,7节),CPLD中有多个逻辑块,这些逻辑块之间可以使用可编程内部连线实现相互连接。为了增强对I/0的控制能力,提高引脚的适应性,CPLD中还增加了I/o控制块。每个I/0块中有若干个I/o单元。

可编程乘积项阵,乘积项阵列有汜个输入,可以产生而变量的乘积项。一般一个宏单元对应5个乘积项,这样,在逻辑块中共有5×屁个乘积项。例如,XC9500系列的逻辑块中有90个36变量乘积项,MAX7000系列的逻辑块中有80个36变量乘积项。

乘积项分配和宏单元,不同型号的CPLD器件,乘积项分配和宏单元电路结构也不完全相同,但所要实现的功能大体相似。为XC9500系列的乘积项分配和宏单元电路。图中S1~S:为可编程数据分配器,M1~M5为可编程数据选择器。为简明起见,没有画出它们的可编程选择输入端。

或下一个宏单元去。这种乘积项的“链式”结构,可以实现远远多于5个乘积项的与一或式。在XC9500系列CPLD中,理论上可以将90个乘积项组合到一个宏单元中,产生90个乘积项的与一或式,但此时其余17个宏单元将不能使用乘积项了。在Altera公司生产的CPLD中,宏单元中除了有乘积项扩展功能外,还有乘积项共享电路,使得同一个乘积项可以被多个宏单元同时使用。

数据分配器S1~S5中间输出的乘积项用于特殊功能,这些功能包括作为触发器FF的置位、复位、时钟信号,异或门G5的同相/反相输出控制信号和乘积项输出使能控制信号PrOE。

或门G4输出的与一或式送至异或门G5,G5的另一输入来自数据选择器M1。通过对M1的编程,可以选择0、1或另一个乘积项,来控制G4的输出经G5是否反相,或受另一个乘积项控制。M3可以选择是直接组合形式输出还是经过触发器的寄存器形式输出,触发器FF可以被编程为D触发器或r触发器,且通过M2和M5可以选择全局或乘积项置位、复位信号。通过M4也可以在3个全局时钟和一个乘积项中选择触发器的时钟信号。

宏单元的输出不仅送至I/0单元,还送到内部可编程连线区,以被其他宏单元使用。

深圳市唯有度科技有限公司http://wydkj.51dzw.com/

公网安备44030402000607

公网安备44030402000607