TC648EUA713 延时锁环DLL

发布时间:2019/10/24 12:25:45 访问次数:661

TC648EUA713于555定时器内部的比较器灵敏度较高,而且采用差分电路形式,用555定时器组成的多谐振荡器的振荡频率受电源电压和温度变化的影响很小。

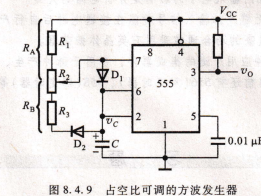

图8.4.8所示电路的tPL≠JpH,而且占空比固定不变。如果要实现占空比可调,可采用如图8.4.9所示电路。由于电路中二极管D1、D2的单向导电特性,使电容器C的充放电回路分开,调节电位器,就可调节多谐振荡器的占空比。图中,ycc通过RA、D1向电容C充电,充电时间为

rpH≈0.7RAC

电容器C通过D2、R:及555中的三极管T放电,放电时间为

tpl=0.7RBC

因而,振荡频率为

F=1/TPH+TPL=1.43/(Ra+rb)c

电路输出波形的占空比为

Q(%)=Ra/ra+rb*100%

图8.4.9 占空比可调的方波发生器

上面仅讨论了由555定时器组成的单稳态触发器、多谐振荡器和施密特触发器,实际上,由于555定时器的比较器灵敏度高、输出驱动电流大、功能灵活,因而在电子电路中获得广泛应用,限于篇幅,这里就不一一列举了。

555定时器具有哪些应用特点?其典型应用电路有哪几种?

555定时器中缓冲器G有什么作用?

如果将图8,4.4(a)中555定时器的控制电压输人端(5脚)改接外部输入电压vr上,试问电路的输出脉宽tw有无改变?tw与vr的关系如何?

能否采用改变图8.4.5中555定时器控制电压的方法调节电路的振荡频率?

部引脚数据与内部数据进行交换的接口电路,通过编程可将I/0引脚设置成输入、输出和双向等不同的功能。IOB分布在芯片的四周。

延时锁环DLL可以控制和修正内部各部分时钟的传输延迟时间,保证逻辑电路可靠地工作。同时,也可以产生相位滞后0°、90°、180°和270°的时钟脉冲,还可产生倍频或分频时钟,分频系数可以是1.5、2、2.5、3、4、5、8、16等。

CLB之间的空隙部分是布线区①,分布着可编程布线资源。通过它们实现CLB与CLB之间、CLB与IOB之间以及全局时钟等信号与CLB和IOB之间的连接。

在Xilinx公司的高性能产品中,已将乘法器、数字信号处理器等集成在FPGA中,大大增强了FPGA的功能。同时,为了使芯片稳定可靠地工作,其内部都设有数字时钟管理模块。由于这些内容已超出本书讨论范围,所以此处只介绍FPGA中几个最基本的功能模块。

可编程逻辑模块CLB

CLB是FPGA中的基本逻辑模块,它可实现绝大多数的逻辑功能,其简化的原理框图如图7.4.5所示。构成CLB的基础是逻辑单元(LC②),一个LC中包括一个4输人LUT、进位及控制逻辑和一个D触发器(EC为时钟使能控制端)。每个CLB包含4个LC,并将每2个LC组织在1个微片(slice)中,图中可见有2个微片。在Virtex-Ⅱ和Spartan-3系列中,CLB包含有4个微片,即含有8个LC。CLB的输入来自可编程布线区,其输出再回送到内部布线区。图7.4.5 Spartan-Ⅱ、Ⅴirtex系列简化的CLB原理框图.

实际上,「PGA采用多层布局布线结构,并非只能在模块间的空隙处布线。

Logic Cell的缩写。

TC648EUA713于555定时器内部的比较器灵敏度较高,而且采用差分电路形式,用555定时器组成的多谐振荡器的振荡频率受电源电压和温度变化的影响很小。

图8.4.8所示电路的tPL≠JpH,而且占空比固定不变。如果要实现占空比可调,可采用如图8.4.9所示电路。由于电路中二极管D1、D2的单向导电特性,使电容器C的充放电回路分开,调节电位器,就可调节多谐振荡器的占空比。图中,ycc通过RA、D1向电容C充电,充电时间为

rpH≈0.7RAC

电容器C通过D2、R:及555中的三极管T放电,放电时间为

tpl=0.7RBC

因而,振荡频率为

F=1/TPH+TPL=1.43/(Ra+rb)c

电路输出波形的占空比为

Q(%)=Ra/ra+rb*100%

图8.4.9 占空比可调的方波发生器

上面仅讨论了由555定时器组成的单稳态触发器、多谐振荡器和施密特触发器,实际上,由于555定时器的比较器灵敏度高、输出驱动电流大、功能灵活,因而在电子电路中获得广泛应用,限于篇幅,这里就不一一列举了。

555定时器具有哪些应用特点?其典型应用电路有哪几种?

555定时器中缓冲器G有什么作用?

如果将图8,4.4(a)中555定时器的控制电压输人端(5脚)改接外部输入电压vr上,试问电路的输出脉宽tw有无改变?tw与vr的关系如何?

能否采用改变图8.4.5中555定时器控制电压的方法调节电路的振荡频率?

部引脚数据与内部数据进行交换的接口电路,通过编程可将I/0引脚设置成输入、输出和双向等不同的功能。IOB分布在芯片的四周。

延时锁环DLL可以控制和修正内部各部分时钟的传输延迟时间,保证逻辑电路可靠地工作。同时,也可以产生相位滞后0°、90°、180°和270°的时钟脉冲,还可产生倍频或分频时钟,分频系数可以是1.5、2、2.5、3、4、5、8、16等。

CLB之间的空隙部分是布线区①,分布着可编程布线资源。通过它们实现CLB与CLB之间、CLB与IOB之间以及全局时钟等信号与CLB和IOB之间的连接。

在Xilinx公司的高性能产品中,已将乘法器、数字信号处理器等集成在FPGA中,大大增强了FPGA的功能。同时,为了使芯片稳定可靠地工作,其内部都设有数字时钟管理模块。由于这些内容已超出本书讨论范围,所以此处只介绍FPGA中几个最基本的功能模块。

可编程逻辑模块CLB

CLB是FPGA中的基本逻辑模块,它可实现绝大多数的逻辑功能,其简化的原理框图如图7.4.5所示。构成CLB的基础是逻辑单元(LC②),一个LC中包括一个4输人LUT、进位及控制逻辑和一个D触发器(EC为时钟使能控制端)。每个CLB包含4个LC,并将每2个LC组织在1个微片(slice)中,图中可见有2个微片。在Virtex-Ⅱ和Spartan-3系列中,CLB包含有4个微片,即含有8个LC。CLB的输入来自可编程布线区,其输出再回送到内部布线区。图7.4.5 Spartan-Ⅱ、Ⅴirtex系列简化的CLB原理框图.

实际上,「PGA采用多层布局布线结构,并非只能在模块间的空隙处布线。

Logic Cell的缩写。

上一篇:STM8319 整形及定时

热门点击

热门点击

- LA5112N 复杂的数字系统制作

- 7次谐波的实用判据

- MAX6805US44D3+T CMOS集成

- LM4852LQ MOS管的开关特性

- LM116H/883C CMOS门电路是否过

- TW9919 集成电路编码器

- ISL9206ADRTZ 漏极开路CMOS

- TA7155P 电感电路中时间常数

- 制作灯光光晕效果

- MB3771PF-G-BND-NH-ER 逻

推荐技术资料

推荐技术资料

- 泰克新发布的DSA830

- 泰克新发布的DSA8300在一台仪器中同时实现时域和频域分析,DS... [详细]

公网安备44030402000607

公网安备44030402000607