TLP421-1F(P/B)LUTЮЊ4ЪфШыНсЙЙ

ЗЂВМЪБМф:2019/10/24 12:26:15 ЗУЮЪДЮЪ§:1268

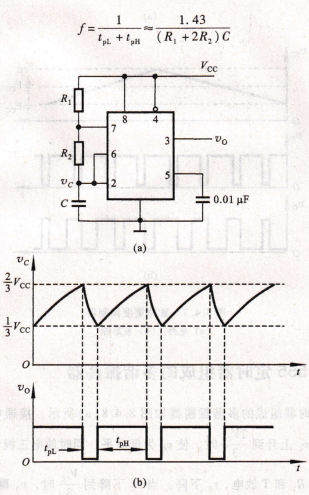

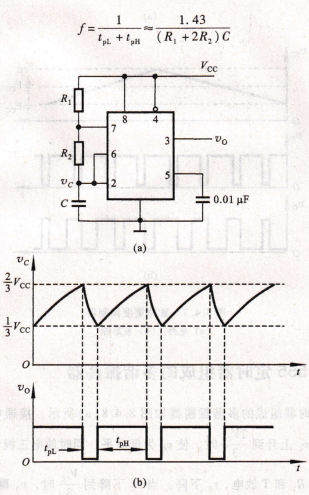

TLP421-1F(P/B)гУ555ЖЈЪБЦїзщГЩЕФЖраГеёЕДЦїШчЭМ8.4.8(a)ЫљЪО ЁЃНгЭЈЕчдДКѓ ,ЕчШнCБЛГфЕч ,ЕБvcЩЯЩ§ЕН2vcc/3ЪБЃЌЪЙv0ЮЊЕЭЕчЦН ,ЭЌ 0ЪБЗХЕчШ§МЋЙм 0TЕМЭЈ ,ДЫЪБЕчШнCЭЈЙ§R2КЭTЗХЕч ,vcЯТНЕЁЃЕБЮ№cЯТНЕЕНИЪЪБ ,v0ЗзЊЮЊИпЕчЦН ЁЃЕчШнЦїCЗХЕчЫљашЕФЪБМфЮЊНгЭЈЕчдДКѓ,ЕчШнЕчШ§МЋЙмTЕМЭЈ,ДЫЪБЕчШнCЭЈЙ§R2КЭTЗХЕч,vcЯТНЕЁЃЕБvcЯТНЕЕНИЪЪБ,vЁЃЗзЊЮЊИпЕчЦНЁЃЕчШнЦїCЗХЕчЫљашЕФЪБМфЮЊЖјЪЧВЩгУВщЮвБэ(LUTЂй)ЪЕЯжТпМКЏЪ§ЁЃетжжВЛЭЌгкCPLDНсЙЙЕФЬиЕу,ЪЙFPGAжаПЩвдАќКЌЪ§СПжкЖрЕФLUTКЭДЅЗЂЦї,ДгЖјФмЙЛЪЕЯжИќДѓЙцФЃЁЂИќИДдгЕФТпМЕчТЗ,БмУтСЫЁАгы-ЛђЁБеѓСаНсЙЙЩЯЕФЯожЦКЭДЅЗЂЦїМАyoЖЫЪ§СПЩЯЕФЯожЦЁЃ

НќФъРД,ЩњВњЙЄвеЩЯЕФНјВНДѓДѓНЕЕЭСЫFPGAЕФГЩБО,ЦфЙІФмМАадФмЩЯЕФгХдНадИќЮЊЭЛГіЁЃвђДЫ,FPGAвбГЩЮЊФПЧАЩшМЦЪ§зжЕчТЗЛђЯЕЭГЕФЪзбЁЦїМўжЎвЛЁЃ

ЖдгІЕФФкШнЪфГі,дкFЖЫБуЕУЕНИУзщЪфШЫаХКХТпМдЫЫу,евГіЕижЗЕБгУЛЇЭЈЙ§дРэЭМЛђHDLгябдУшЪіСЫвЛИіТпМЕчТЗМўЛсздЖЏМЦЫуТпМЕчТЗЕФЫљгаПЩФмЕФНсЙћ(ецжЕБэ),ВЂАбвдКѓ,FPGAПЊЗЂШэНсЙћаДШыSRAM,етвЛЙ§ГЬОЭЪЧЫљЮНЕФБрГЬЁЃДЫКѓ,SRAMжаЕФФкШнЪМжеБЃГжВЛБф,LUTОЭОпгаСЫШЗЖЈЕФТпМЙІФмЁЃгЩгкSRAMОпгаЪ§ОнвзЪЇад,МДвЛЕЉЖЯЕч,ЦфдгаЕФТпМЙІФмНЋЯћЪЇЁЃЫљвдFPGAвЛАуашвЊвЛИіЭтВПЕФPROMБЃДцБрГЬЪ§ОнЁЃЩЯЕчКѓ,FPGAЪзЯШДгPROMжаЖСШЫБрГЬЪ§ОнНјааГѕЪМЛЏ,ШЛКѓВХПЊЪМе§ГЃЙЄзїЁЃ

гЩгквЛАуЕФLUTЮЊ4ЪфШыНсЙЙ,Ыљвд,ЕБвЊЪЕЯжЖргк4БфСПЕФТпМКЏЪ§ЪБ,ОЭашвЊгУЖрИіLUTМЖСЊРДЪЕЯжЁЃвЛАуFPGAжаЕФLUTЪЧЭЈЙ§Ъ§ОнбЁдёЦїЭъГЩМЖСЊЕФЁЃЭМ7.4.2ЫљЪОЪЧгЩ4ИіLUTКЭШєИЩИі2бЁ1Ъ§ОнбЁдёЦїЪЕЯж6БфСПШЮвтТпМКЏЪ§ЕФдРэЭМЁЃИУЕчТЗЪЕМЪЩЯНЋ4Иі16ЁС1ЮЛЕФLUTРЉеЙГЩЮЊ64ЁС1ЮЛЁЃAЁЂBЯрЕБгк6ЮЛЕижЗЕФзюИп2ЮЛ,ЫќУЧШЁВЛЭЌжЕЪБ,ЪфГігыLUTЕФЙиЯЕШчБэ7.4.2ЫљЪОЁЃ

БфСПТпМКЏЪ§дкLUTЩЯдйдіМгДЅЗЂЦї,МЙІФмгжПЩЪЕЯжЪБађТпМЙІФмЕФЛљБОТпМЕЅдЊЕчТЗетбљЕФЛљБОТпМЕЅдЊРДЪЕЯжИїжжИДдгТпМЙІФмЕФЁЃ

ПЩБрГЬЪ§ОнбЁдёЦїMUЂњ,(aЁЕПЩБрГЬЫФбЁвЛMUX (b)ПЩБрГЬMUXМђЛЏЗћКХ,ПЩБрГЬЪ§ОнбЁдёЦїMUXдкFPGAжавВГфЕБзХживЊНЧЩЋЁЃР§Шч,дкЭМ7,4,3(a)жа,БрГЬЪБдкSRAMДцДЂЕЅдЊM1ЁЂM2жааДШы0Лђ1,ОЭПЩвдШЗЖЈБЛбЁжаЕФЪфШЫЭЈЕРгыЪфГіЯрСЌЁЃДЫЪБMUXОЭЪЧПЩБрГЬЕФЪ§ОнПЊЙи,БрГЬКѓ,ПЊЙиЕФЮЛжУвВОЭШЗЖЈСЫЁЃЮЊМђУїЦ№Мћ,дкFPGAТпМЭМжа,ЭЈГЃВЩгУЭМ7.4.3(b)ЫљЪОЕФМђЛЏЗћКХЁЃ

гЩгкSRAMжаЕФЪ§ОнРэТлЩЯПЩвдНјааЮоЯоДЮаДШЫ,Ыљвд,ЛљгкSRAMММЪѕЕФFPGAПЩвдНјааЮоЯоДЮЕФБрГЬЁЃ

FPGAЕФНсЙЙ,ФПЧА,ЫфШЛFPGAВњЦЗжжРрНЯЖр,ЕЋXilinxЙЋЫОЕФFPGAзюЮЊЕфаЭЁЃетРявдИУЙЋЫОЕФВњЦЗЮЊР§,НщЩмFPGAЕФФкВПНсЙЙМАИїФЃПщЕФЙІФмЁЃ

FPGAЕФНсЙЙЪОвтЭМШчЭМ7,4.4ЫљЪОЁЃЫќжївЊгЩПЩБрГЬТпМФЃПщ(CLBЂй)ЁЂRAMПщ(Bbck RAM)ЁЂЪфШы/ЪфГіФЃПщ(IOBЂк)ЁЂбгЪБЫјЛЗ(DLLЂл)КЭПЩБрГЬВМЯпОиеѓ(PRMЂм,ЭМ7.4.4жаЮДЛ)ЕШзщГЩЁЃFPGAЕФЙцФЃВЛЭЌ,ЦфЫљКЌФЃПщЕФЪ§СПвВВЛЭЌЁЃПЩБрГЬТпМФЃПщCLBЪЧЪЕЯжИїжжТпМЙІФмЕФЛљБОЕЅдЊ,АќРЈзщКЯТпМЁЂЪБађТпМЁЂМгЗЈЦїЕШдЫЫуЙІФмЁЃПЩБрГЬЕФЪфШЫ/ЪфГіФЃПщIOBЪЧаОЦЌЭт.

ЯЕConfigurable Logic BlockЕФЫѕаД,вВГЦЮЊПЩХфжУТпМФЃПщЁЃ

ЯЕInput/output BlockЕФЫѕаДЁЃ

ЯЕDelay-Locked L00pЕФЫѕаДЁЃ

ЯЕProgrammable Routing MaoixЕФЫѕаД.

TLP421-1F(P/B)гУ555ЖЈЪБЦїзщГЩЕФЖраГеёЕДЦїШчЭМ8.4.8(a)ЫљЪО ЁЃНгЭЈЕчдДКѓ ,ЕчШнCБЛГфЕч ,ЕБvcЩЯЩ§ЕН2vcc/3ЪБЃЌЪЙv0ЮЊЕЭЕчЦН ,ЭЌ 0ЪБЗХЕчШ§МЋЙм 0TЕМЭЈ ,ДЫЪБЕчШнCЭЈЙ§R2КЭTЗХЕч ,vcЯТНЕЁЃЕБЮ№cЯТНЕЕНИЪЪБ ,v0ЗзЊЮЊИпЕчЦН ЁЃЕчШнЦїCЗХЕчЫљашЕФЪБМфЮЊНгЭЈЕчдДКѓ,ЕчШнЕчШ§МЋЙмTЕМЭЈ,ДЫЪБЕчШнCЭЈЙ§R2КЭTЗХЕч,vcЯТНЕЁЃЕБvcЯТНЕЕНИЪЪБ,vЁЃЗзЊЮЊИпЕчЦНЁЃЕчШнЦїCЗХЕчЫљашЕФЪБМфЮЊЖјЪЧВЩгУВщЮвБэ(LUTЂй)ЪЕЯжТпМКЏЪ§ЁЃетжжВЛЭЌгкCPLDНсЙЙЕФЬиЕу,ЪЙFPGAжаПЩвдАќКЌЪ§СПжкЖрЕФLUTКЭДЅЗЂЦї,ДгЖјФмЙЛЪЕЯжИќДѓЙцФЃЁЂИќИДдгЕФТпМЕчТЗ,БмУтСЫЁАгы-ЛђЁБеѓСаНсЙЙЩЯЕФЯожЦКЭДЅЗЂЦїМАyoЖЫЪ§СПЩЯЕФЯожЦЁЃ

НќФъРД,ЩњВњЙЄвеЩЯЕФНјВНДѓДѓНЕЕЭСЫFPGAЕФГЩБО,ЦфЙІФмМАадФмЩЯЕФгХдНадИќЮЊЭЛГіЁЃвђДЫ,FPGAвбГЩЮЊФПЧАЩшМЦЪ§зжЕчТЗЛђЯЕЭГЕФЪзбЁЦїМўжЎвЛЁЃ

ЖдгІЕФФкШнЪфГі,дкFЖЫБуЕУЕНИУзщЪфШЫаХКХТпМдЫЫу,евГіЕижЗЕБгУЛЇЭЈЙ§дРэЭМЛђHDLгябдУшЪіСЫвЛИіТпМЕчТЗМўЛсздЖЏМЦЫуТпМЕчТЗЕФЫљгаПЩФмЕФНсЙћ(ецжЕБэ),ВЂАбвдКѓ,FPGAПЊЗЂШэНсЙћаДШыSRAM,етвЛЙ§ГЬОЭЪЧЫљЮНЕФБрГЬЁЃДЫКѓ,SRAMжаЕФФкШнЪМжеБЃГжВЛБф,LUTОЭОпгаСЫШЗЖЈЕФТпМЙІФмЁЃгЩгкSRAMОпгаЪ§ОнвзЪЇад,МДвЛЕЉЖЯЕч,ЦфдгаЕФТпМЙІФмНЋЯћЪЇЁЃЫљвдFPGAвЛАуашвЊвЛИіЭтВПЕФPROMБЃДцБрГЬЪ§ОнЁЃЩЯЕчКѓ,FPGAЪзЯШДгPROMжаЖСШЫБрГЬЪ§ОнНјааГѕЪМЛЏ,ШЛКѓВХПЊЪМе§ГЃЙЄзїЁЃ

гЩгквЛАуЕФLUTЮЊ4ЪфШыНсЙЙ,Ыљвд,ЕБвЊЪЕЯжЖргк4БфСПЕФТпМКЏЪ§ЪБ,ОЭашвЊгУЖрИіLUTМЖСЊРДЪЕЯжЁЃвЛАуFPGAжаЕФLUTЪЧЭЈЙ§Ъ§ОнбЁдёЦїЭъГЩМЖСЊЕФЁЃЭМ7.4.2ЫљЪОЪЧгЩ4ИіLUTКЭШєИЩИі2бЁ1Ъ§ОнбЁдёЦїЪЕЯж6БфСПШЮвтТпМКЏЪ§ЕФдРэЭМЁЃИУЕчТЗЪЕМЪЩЯНЋ4Иі16ЁС1ЮЛЕФLUTРЉеЙГЩЮЊ64ЁС1ЮЛЁЃAЁЂBЯрЕБгк6ЮЛЕижЗЕФзюИп2ЮЛ,ЫќУЧШЁВЛЭЌжЕЪБ,ЪфГігыLUTЕФЙиЯЕШчБэ7.4.2ЫљЪОЁЃ

БфСПТпМКЏЪ§дкLUTЩЯдйдіМгДЅЗЂЦї,МЙІФмгжПЩЪЕЯжЪБађТпМЙІФмЕФЛљБОТпМЕЅдЊЕчТЗетбљЕФЛљБОТпМЕЅдЊРДЪЕЯжИїжжИДдгТпМЙІФмЕФЁЃ

ПЩБрГЬЪ§ОнбЁдёЦїMUЂњ,(aЁЕПЩБрГЬЫФбЁвЛMUX (b)ПЩБрГЬMUXМђЛЏЗћКХ,ПЩБрГЬЪ§ОнбЁдёЦїMUXдкFPGAжавВГфЕБзХживЊНЧЩЋЁЃР§Шч,дкЭМ7,4,3(a)жа,БрГЬЪБдкSRAMДцДЂЕЅдЊM1ЁЂM2жааДШы0Лђ1,ОЭПЩвдШЗЖЈБЛбЁжаЕФЪфШЫЭЈЕРгыЪфГіЯрСЌЁЃДЫЪБMUXОЭЪЧПЩБрГЬЕФЪ§ОнПЊЙи,БрГЬКѓ,ПЊЙиЕФЮЛжУвВОЭШЗЖЈСЫЁЃЮЊМђУїЦ№Мћ,дкFPGAТпМЭМжа,ЭЈГЃВЩгУЭМ7.4.3(b)ЫљЪОЕФМђЛЏЗћКХЁЃ

гЩгкSRAMжаЕФЪ§ОнРэТлЩЯПЩвдНјааЮоЯоДЮаДШЫ,Ыљвд,ЛљгкSRAMММЪѕЕФFPGAПЩвдНјааЮоЯоДЮЕФБрГЬЁЃ

FPGAЕФНсЙЙ,ФПЧА,ЫфШЛFPGAВњЦЗжжРрНЯЖр,ЕЋXilinxЙЋЫОЕФFPGAзюЮЊЕфаЭЁЃетРявдИУЙЋЫОЕФВњЦЗЮЊР§,НщЩмFPGAЕФФкВПНсЙЙМАИїФЃПщЕФЙІФмЁЃ

FPGAЕФНсЙЙЪОвтЭМШчЭМ7,4.4ЫљЪОЁЃЫќжївЊгЩПЩБрГЬТпМФЃПщ(CLBЂй)ЁЂRAMПщ(Bbck RAM)ЁЂЪфШы/ЪфГіФЃПщ(IOBЂк)ЁЂбгЪБЫјЛЗ(DLLЂл)КЭПЩБрГЬВМЯпОиеѓ(PRMЂм,ЭМ7.4.4жаЮДЛ)ЕШзщГЩЁЃFPGAЕФЙцФЃВЛЭЌ,ЦфЫљКЌФЃПщЕФЪ§СПвВВЛЭЌЁЃПЩБрГЬТпМФЃПщCLBЪЧЪЕЯжИїжжТпМЙІФмЕФЛљБОЕЅдЊ,АќРЈзщКЯТпМЁЂЪБађТпМЁЂМгЗЈЦїЕШдЫЫуЙІФмЁЃПЩБрГЬЕФЪфШЫ/ЪфГіФЃПщIOBЪЧаОЦЌЭт.

ЯЕConfigurable Logic BlockЕФЫѕаД,вВГЦЮЊПЩХфжУТпМФЃПщЁЃ

ЯЕInput/output BlockЕФЫѕаДЁЃ

ЯЕDelay-Locked L00pЕФЫѕаДЁЃ

ЯЕProgrammable Routing MaoixЕФЫѕаД.

ЩЯвЛЦЊЃКTNETW5306PYP ЪЇТфТіГхМьВт

ЩЯвЛЦЊЃКTC648EUA713 бгЪБЫјЛЗDLL

ШШУХЕуЛї

ШШУХЕуЛї

- е§ЕчСїдДЁЂИКЕчСїдДгЩЕчСїПЊЙиПижЦ

- СНТЗЪфГіЕчСїЯрЭЌ

- FQP34N20ФТЖћаЭЪБађЕчТЗ

- SG2813J/883B 6Яп-64ЯпвыТыЦї

- SN74HC393NS 16ЮЛШЋГЌЧАНјЮЛВњЩњ

- HA13627ЪфГіЖЫЕФТпМУХ

- SMD2920P300TFМЄРјЗНГЬзщКЭЪфГіЗН

- MAX1232C/EPA ФЃФт

- XC1701LPCЪБађТпМ

- 9T12062A2372BBHFT ЩЋЛЗЕчШн

ЭЦМіММЪѕзЪСЯ

ЭЦМіММЪѕзЪСЯ

- ЛЌбЉШЦзЎЛњЦїШЫ

- БОР§ЪЧвЛПюЗЧГЃгаШЄЃЌЭЌЪБгжгавЛЖЈЕїЪдФбЖШЕФЭцЗЈЁЃEDE2116AB... [ЯъЯИ]

- ИпадФм 32 ЮЛ RISC-V

- ШЋаТЮоЯпЭЈаХФЃзщЁЊ ML321

- 6ФЩУзжЦГЬЩфЦЕЃЈRFЃЉКЭРЖбРЯШ

- ЯШНјаОЦЌКЭЙІТЪаОЦЌЪаГЁашЧѓМАЗЂ

- КЃЫМСшЯіЭјТч760НтОіЗНАИНтЖС

- аТаЭЮоЯпЖЬОрЭЈаХаЧЩСММЪѕЃЈNe

- ЖрУНЬхаДІРэЦїSM501дкЧЖШыЪНЯЕЭГжаЕФгІгУ

- ЛљгкIEEE802.11bЕФEPAЮТЖШБфЫЭЦї

- QUICCEngineаТв§ЧцЭЦЖЏIPЭјТчИяаТ

- SoCУцЪРАЫФъКѓЕФВњвЕЛњгі

- MPC8xxЯЕСаДІРэЦїЕФЧЖШыЪНЯЕЭГЕчдДЩшМЦ

- dsPICМАЦфдкНЛСїБфЦЕЕїЫйжаЕФгІгУбаОП

ЙЋЭјАВБИ44030402000607

ЙЋЭјАВБИ44030402000607