T350B475K016AS �ٻ���洢��

����ʱ��:2019/10/21 8:39:57 ���ʴ���:467

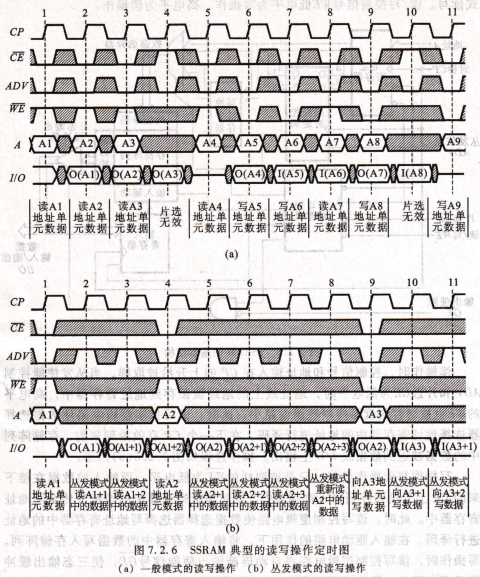

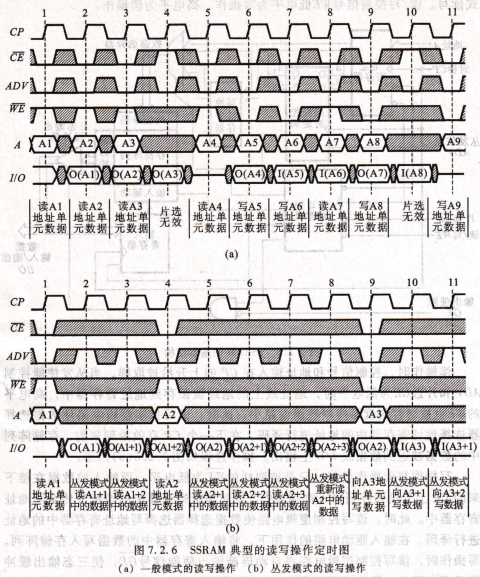

T350B475K016AS��ģʽ�Ķ�д���� (b)�Է�ģʽ�Ķ�д����

ע:ͼ�м������ʹ���ź�0Eʼ����Ч(�͵�ƽ)��0(A1)��ʾAl��ַ��Ԫ�е�����,������,������r/o���ϡ�I(A1)���ʾ��Al��ַ��Ԫд�˵����ݳ����ڡ�o���ϡ�ʵ����,J/o���ϵ�������ǰһ��CP�����õĽ����A1+1��ʾ��A1��ַ������,�ɴԷ������������ĵ�һ����ַ,A1+2��ʾ�ɴԷ������������ĵڶ�����ַ,�����ơ�

��ʱ,�ɴԷ�����������һ��A1����������,����������һ����ַ��AIAO������/д�����ڴԷ���������2λ������,������ADy���ָߵ�ƽʱ,������������4����ͬ�ĵ�ַ��sSRAM�����ִԷ�ģʽ,��������/д�����ʱ,���������ⲿ��ַ���ߵ�ռ��ʱ��,��߶�дЧ�ʡ���/дʱ,ÿ4����һ��,����ֻ���ṩ��ַ,����3����ַ��ssRAM�ڲ��Է��������������������4��ʱ�������Ա��ִԷ�ģʽ(�������µ��ⲿ��ַ),�Է�������ѭ�������ĵ�ַ���ж�/д�������Է�ģʽ�Ķ�д����������ͼ7.2.6(b)��ʾ��

����sSRAM���ɵļ����ϵͳ��,������ʱ����Ч�ص���ʱ,��ַ�����ݡ����Ƶ��źű����浽ssRAM�ڲ��ļĴ�����,��˶�д���̵���ʱ�ȴ�����ʱ����������sSRAM�ڲ�������ɡ���ʱ,ϵͳ�е��������ڶ�дsSRAM��ͬʱ,���Դ�����������,�Ӷ����������ϵͳ�Ĺ����ٶȡ�����,����sSRAM������ʱ��ͬ���ķ�ʽ����,��˿��Խ���д���̵ĸ�����ʱ�����Ż����,��������оƬ�ڲ�,ʹ��sSRAM�Ķ�д�ٶȸ���SRAM��

sSRAM������ͬ��������ʽҲʹ��Ӧ�ø���㡣�û�ʹ��ʱ,���е������ź�ֻҪΧ��ʱ�ӵ���Ч�ؽ�����Ƽ��ɡ����,ĿǰssRAM�ѹ㷺Ӧ���ڸ���ͬ������������ϵͳ��,�ر����봦����һͬ������ϵͳ,������˵����еij����ٻ���洢��(Cache)��

����SSRAM,���ż���������������ҵ(���绥����)�Ŀ��ٷ�չ,�Դ洢������˸��ߵ�Ҫ���١����ܶȡ��������ѳ�ΪRAM��չ���������⡣��ss-RAM֮��,����RAM�������Ⱥ���˫�����ݴ����ʾ�̬�����ȡ�洢��

(DDR��SRAM)���ı����ݴ����ʾ�̬�����ȡ�洢��(QDR��SRAM)��

����sSRAMֻ��ʱ�ӵ������ش�������,���ҹ��ö�/д��������,����дֻ�ܷ�ʱ���С�����sSRAMҲ��Ϊ�������ݴ����ʾ�̬�����ȡ�洢��(SDR��SRAM)��DDR SRAM����ssRAM�����Ͼ����Ľ�,��ÿ��ʱ�����ڵ������غ��½��ظ�����һ������,�������ݴ���Ч�������һ��,���Ƕ�д�Բ���ͬʱ���С�

QDR SRAM��һ���Ľ��˽ṹ,Ϊ����д�����ֱ��ṩ�����Ľӿ�,������ÿ��ʱ�����ڵ������غ��½��ع�������������,����ÿ�ζ�д�ܹ�ͬʱ����,�������������ߵ�����,ʹ���ݴ���Ч�������ssRAM�����������

��DDR��QDRijЩ���ܽ��и��ƺ�IJ�Ʒ��ΪDDR ���QDR �� SRAM��Ŀǰ,����0.09 um���ռ���������SRAM��������Ѵ�72 Mbit,���ʱ�ӹ���Ƶ�ʴﵽ333 MHz��

��7.2.2��ʾΪ����SRAM��Ʒ�ļ�����Ҫָ�ꡣ

ϵDouble Data Rate����д��

ϵQuad Data Rate����д.

ϵSinglc Data Rate����д��

T350B475K016AS��ģʽ�Ķ�д���� (b)�Է�ģʽ�Ķ�д����

ע:ͼ�м������ʹ���ź�0Eʼ����Ч(�͵�ƽ)��0(A1)��ʾAl��ַ��Ԫ�е�����,������,������r/o���ϡ�I(A1)���ʾ��Al��ַ��Ԫд�˵����ݳ����ڡ�o���ϡ�ʵ����,J/o���ϵ�������ǰһ��CP�����õĽ����A1+1��ʾ��A1��ַ������,�ɴԷ������������ĵ�һ����ַ,A1+2��ʾ�ɴԷ������������ĵڶ�����ַ,�����ơ�

��ʱ,�ɴԷ�����������һ��A1����������,����������һ����ַ��AIAO������/д�����ڴԷ���������2λ������,������ADy���ָߵ�ƽʱ,������������4����ͬ�ĵ�ַ��sSRAM�����ִԷ�ģʽ,��������/д�����ʱ,���������ⲿ��ַ���ߵ�ռ��ʱ��,��߶�дЧ�ʡ���/дʱ,ÿ4����һ��,����ֻ���ṩ��ַ,����3����ַ��ssRAM�ڲ��Է��������������������4��ʱ�������Ա��ִԷ�ģʽ(�������µ��ⲿ��ַ),�Է�������ѭ�������ĵ�ַ���ж�/д�������Է�ģʽ�Ķ�д����������ͼ7.2.6(b)��ʾ��

����sSRAM���ɵļ����ϵͳ��,������ʱ����Ч�ص���ʱ,��ַ�����ݡ����Ƶ��źű����浽ssRAM�ڲ��ļĴ�����,��˶�д���̵���ʱ�ȴ�����ʱ����������sSRAM�ڲ�������ɡ���ʱ,ϵͳ�е��������ڶ�дsSRAM��ͬʱ,���Դ�����������,�Ӷ����������ϵͳ�Ĺ����ٶȡ�����,����sSRAM������ʱ��ͬ���ķ�ʽ����,��˿��Խ���д���̵ĸ�����ʱ�����Ż����,��������оƬ�ڲ�,ʹ��sSRAM�Ķ�д�ٶȸ���SRAM��

sSRAM������ͬ��������ʽҲʹ��Ӧ�ø���㡣�û�ʹ��ʱ,���е������ź�ֻҪΧ��ʱ�ӵ���Ч�ؽ�����Ƽ��ɡ����,ĿǰssRAM�ѹ㷺Ӧ���ڸ���ͬ������������ϵͳ��,�ر����봦����һͬ������ϵͳ,������˵����еij����ٻ���洢��(Cache)��

����SSRAM,���ż���������������ҵ(���绥����)�Ŀ��ٷ�չ,�Դ洢������˸��ߵ�Ҫ���١����ܶȡ��������ѳ�ΪRAM��չ���������⡣��ss-RAM֮��,����RAM�������Ⱥ���˫�����ݴ����ʾ�̬�����ȡ�洢��

(DDR��SRAM)���ı����ݴ����ʾ�̬�����ȡ�洢��(QDR��SRAM)��

����sSRAMֻ��ʱ�ӵ������ش�������,���ҹ��ö�/д��������,����дֻ�ܷ�ʱ���С�����sSRAMҲ��Ϊ�������ݴ����ʾ�̬�����ȡ�洢��(SDR��SRAM)��DDR SRAM����ssRAM�����Ͼ����Ľ�,��ÿ��ʱ�����ڵ������غ��½��ظ�����һ������,�������ݴ���Ч�������һ��,���Ƕ�д�Բ���ͬʱ���С�

QDR SRAM��һ���Ľ��˽ṹ,Ϊ����д�����ֱ��ṩ�����Ľӿ�,������ÿ��ʱ�����ڵ������غ��½��ع�������������,����ÿ�ζ�д�ܹ�ͬʱ����,�������������ߵ�����,ʹ���ݴ���Ч�������ssRAM�����������

��DDR��QDRijЩ���ܽ��и��ƺ�IJ�Ʒ��ΪDDR ���QDR �� SRAM��Ŀǰ,����0.09 um���ռ���������SRAM��������Ѵ�72 Mbit,���ʱ�ӹ���Ƶ�ʴﵽ333 MHz��

��7.2.2��ʾΪ����SRAM��Ʒ�ļ�����Ҫָ�ꡣ

ϵDouble Data Rate����д��

ϵQuad Data Rate����д.

ϵSinglc Data Rate����д��

��һƪ��TMOV20R300M �����Ӧ��

�������

�������

- ��Բ�ɽ��ܶȲ��ԣ�WAT��

- HA1-5104 �����ٽ籥�͵���

- �ڲ����غ������ѹһʱ���ͷֶ������ʱ

- �����Ƶ�pcb�����溸����ƬԪ��

- ��ͳ�ĵ���ӵع���ѡ�߾�������5��г��

- ��������DS18B20�������¶ȴ�����

- ��ѹһʱ���ͷֶ����IJ���

- G��TD-SCDMA��ʹ����Ϊ�ҹ��ƶ�ͨ��

- TMS320F206��FLASH��¼����

- WiFi 6 ·���������dz�

�Ƽ���������

�Ƽ���������

- Seeed Studio

- Seeed Studio����ǵ�ӡ�����Ǻͻ滭���벻��... [��ϸ]

��������44030402000607

��������44030402000607