WD61C197CTV 时序逻辑电路的模型与分类

发布时间:2019/10/17 12:04:39 访问次数:1260

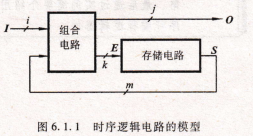

WD61C197CTV时序电路的模型,上述电梯控制的实例可以用如图6.1.1所示时序电路的一般化模型来表示。从总体上看,整个时序电路由进行逻辑运算的组合电路和起记忆作用的存储电路两部分构成,存储电路可用触发器或锁存器组成。为了方便,图中各组变量均以向量表示,其中,r=(r”几,…,fi)为时序电路的输人信号,0=(01,02,…, 图6.1.1 时序逻辑电路的模型a`)为时序电路的输出信号,E=(E”E2,…,E滋)为驱动存储电路转换为下一状态的激励信号,而s=(s1,S2,…,sm)为存储电路的状态信号,亦称为状态变量,它表示时序电路当前的状态,简称现态。状态变量s被反馈到组合电路的输人端,与输入信号r一起决定时序电路的输出信号o,并产生对存储电路的激励信号召,从而确定其下一状态,即次态。于是,上述4组变量间的逻辑关系可用下列三个向量函数形式的方程来表达

o=f・(r,s) (6.1.1)

e=g(r,s) (6・1・2)

sn+1=h(E,s′)) (6.1,3)

式(6.1.1)表达了时序电路的输出信号与输人信号、状态变量的关系,称为时序电路的输出方程。式(6.1,2)表达了激励信号与输入信号、状态变量的关系,称为激励方程。而式(6.1.3)表达了存储电路从现态到次态的转换,故称为状态转换方程,简称状态方程。式(6.1.3)等号右边的S″表示存储电路的现态,而左边s″+1是存储电路的次态,分别以尼和″+1作为上标,以示区别。上述三个向量函数形式的方程分别对应于表达时序电路的三个方程组:输出方程组、激励方程组和状态方程组。

如上所述,时序电路是状态依赖的,故又称为状态机。本章将只限于讨论有限数量的存储单元构成的状态机,因而其状态数也是有限的,称为有限状态机(FSM①)。

时序逻辑电路具有以下主要特征:

时序逻辑电路由组合电路和存储电路组成。

时序逻辑电路的状态与时间因素相关,即时序电路在任一时刻的状态变量不仅是当前输人信号的函数,而且还是电路以前状态的函数,时序电路的输出信号由输人信号和电路的状态共同决定。

异步时序电路与同步时序电路,时序电路可分为异步时序电路和同步时序电路两大类。

若电路中触发器的时钟输入端没有接在统一的时钟脉冲上,或电路中没有时钟脉冲(如SR锁存器构成的时序电路),电路中各存储单元的状态更新不是同时发生的,则这种电路称为异步时序电路。根据电路是对脉冲边沿敏感还是对电平敏感,异步时序电路又分为脉冲异步时序电路(由触发器构成)和电平异步时序电路(由锁存器构成)两种。异步时序电路的状态转换取决于以任意时间间隔变化的输入信号序列,各存储单元的状态转换因存在时间差异而可能造成输出状态短时间的不稳定,而且这种不稳定的状态有时是难以预知的,常常给电路设计和调试带来困难。

WD61C197CTV时序电路的模型,上述电梯控制的实例可以用如图6.1.1所示时序电路的一般化模型来表示。从总体上看,整个时序电路由进行逻辑运算的组合电路和起记忆作用的存储电路两部分构成,存储电路可用触发器或锁存器组成。为了方便,图中各组变量均以向量表示,其中,r=(r”几,…,fi)为时序电路的输人信号,0=(01,02,…, 图6.1.1 时序逻辑电路的模型a`)为时序电路的输出信号,E=(E”E2,…,E滋)为驱动存储电路转换为下一状态的激励信号,而s=(s1,S2,…,sm)为存储电路的状态信号,亦称为状态变量,它表示时序电路当前的状态,简称现态。状态变量s被反馈到组合电路的输人端,与输入信号r一起决定时序电路的输出信号o,并产生对存储电路的激励信号召,从而确定其下一状态,即次态。于是,上述4组变量间的逻辑关系可用下列三个向量函数形式的方程来表达

o=f・(r,s) (6.1.1)

e=g(r,s) (6・1・2)

sn+1=h(E,s′)) (6.1,3)

式(6.1.1)表达了时序电路的输出信号与输人信号、状态变量的关系,称为时序电路的输出方程。式(6.1,2)表达了激励信号与输入信号、状态变量的关系,称为激励方程。而式(6.1.3)表达了存储电路从现态到次态的转换,故称为状态转换方程,简称状态方程。式(6.1.3)等号右边的S″表示存储电路的现态,而左边s″+1是存储电路的次态,分别以尼和″+1作为上标,以示区别。上述三个向量函数形式的方程分别对应于表达时序电路的三个方程组:输出方程组、激励方程组和状态方程组。

如上所述,时序电路是状态依赖的,故又称为状态机。本章将只限于讨论有限数量的存储单元构成的状态机,因而其状态数也是有限的,称为有限状态机(FSM①)。

时序逻辑电路具有以下主要特征:

时序逻辑电路由组合电路和存储电路组成。

时序逻辑电路的状态与时间因素相关,即时序电路在任一时刻的状态变量不仅是当前输人信号的函数,而且还是电路以前状态的函数,时序电路的输出信号由输人信号和电路的状态共同决定。

异步时序电路与同步时序电路,时序电路可分为异步时序电路和同步时序电路两大类。

若电路中触发器的时钟输入端没有接在统一的时钟脉冲上,或电路中没有时钟脉冲(如SR锁存器构成的时序电路),电路中各存储单元的状态更新不是同时发生的,则这种电路称为异步时序电路。根据电路是对脉冲边沿敏感还是对电平敏感,异步时序电路又分为脉冲异步时序电路(由触发器构成)和电平异步时序电路(由锁存器构成)两种。异步时序电路的状态转换取决于以任意时间间隔变化的输入信号序列,各存储单元的状态转换因存在时间差异而可能造成输出状态短时间的不稳定,而且这种不稳定的状态有时是难以预知的,常常给电路设计和调试带来困难。

上一篇:XC1701LPC时序逻辑

上一篇:UPD9602序电路的分析方法

公网安备44030402000607

公网安备44030402000607