M50560-003GP锁存器的翻转时间

发布时间:2019/10/16 17:54:00 访问次数:1104

M50560-003GP利用传输延迟的触发器

工作原理,利用传输延迟的JK触发器的逻辑电路

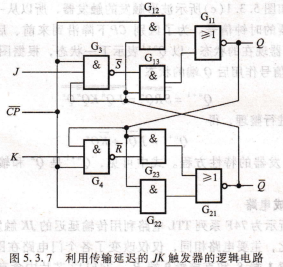

图5.3.7所示为一种利用传输延迟实现的JK触发器电路结构。该电路由Gn、 G12、 G13和G21、 G22、 G23构成两个与或非门 ,这两个与或非门构成sR锁存器作为触发器的输出电路 ,而G3和G4两个与非门则构成触发器的输入电路接收输人信号J Κ 。另外 ,在集成电路的工艺上保证G3和G4门的传输延迟时间大于sR锁存器的翻转时间。

图 5,3.7中的触发器工作原理如下 :

CP=0时 ,一方面G12、G22被CP信号封锁 ,另一方面 ,G3、 G4也被CP封锁 ,不 论J、Κ为何状态,s、R均为1,于是 ,把G” 、G23打开 ,使Gn和G21形成交叉耦合的保持状态,输出 0、 刁状态不变 ,触发器处于稳定状态。

CP由0变1后瞬间,G12、G22两门传输延迟时间较短,抢先打开,Gn和G21继续处于锁定状态,输出仍保持不变。经过一段延迟,s、R才反映使出输人信号J、Κ的作用。设CP由0到1跳变前触发器的状态为O,根据图5.3.7,在此后的CP=1期间

Q=CP* Qn+s・Qn=QN

Q=CP・On+R。qn=0n (5・3・3)

说明触发器状态仍与CP跳变前相同。同时

s=CP・J・On=0n (5・3・4)

R=CP・Κ・On=K0 (5.3.5)

无论J、Κ为何值,若on=1,则从式(5.3.4)可得S=1;反之,On=0,则从式(5.3.5)可得R=1;即s、R不可能同时为0。电路已接收输入信号J、Κ,为触发器状态刷新做好了准备。

M50560-003GP利用传输延迟的触发器

工作原理,利用传输延迟的JK触发器的逻辑电路

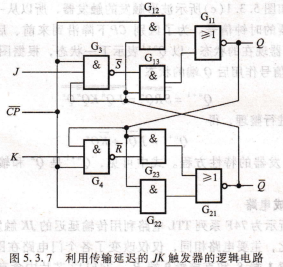

图5.3.7所示为一种利用传输延迟实现的JK触发器电路结构。该电路由Gn、 G12、 G13和G21、 G22、 G23构成两个与或非门 ,这两个与或非门构成sR锁存器作为触发器的输出电路 ,而G3和G4两个与非门则构成触发器的输入电路接收输人信号J Κ 。另外 ,在集成电路的工艺上保证G3和G4门的传输延迟时间大于sR锁存器的翻转时间。

图 5,3.7中的触发器工作原理如下 :

CP=0时 ,一方面G12、G22被CP信号封锁 ,另一方面 ,G3、 G4也被CP封锁 ,不 论J、Κ为何状态,s、R均为1,于是 ,把G” 、G23打开 ,使Gn和G21形成交叉耦合的保持状态,输出 0、 刁状态不变 ,触发器处于稳定状态。

CP由0变1后瞬间,G12、G22两门传输延迟时间较短,抢先打开,Gn和G21继续处于锁定状态,输出仍保持不变。经过一段延迟,s、R才反映使出输人信号J、Κ的作用。设CP由0到1跳变前触发器的状态为O,根据图5.3.7,在此后的CP=1期间

Q=CP* Qn+s・Qn=QN

Q=CP・On+R。qn=0n (5・3・3)

说明触发器状态仍与CP跳变前相同。同时

s=CP・J・On=0n (5・3・4)

R=CP・Κ・On=K0 (5.3.5)

无论J、Κ为何值,若on=1,则从式(5.3.4)可得S=1;反之,On=0,则从式(5.3.5)可得R=1;即s、R不可能同时为0。电路已接收输入信号J、Κ,为触发器状态刷新做好了准备。

公网安备44030402000607

公网安备44030402000607