RNCF0805BTE215R TN�ܿ����ź�

����ʱ��:2019/10/12 17:53:32 ���ʴ���:1349

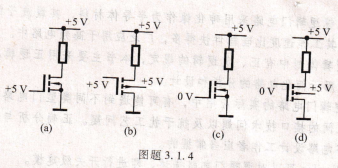

RNCF0805BTE215RVerilog�������ùؼ���cm��s�����˻���������Ԫ��ģ��,����һ������ˡ�һ�����˶˺��������ƶ�,��ͼ3.1.26��ʾ,ϰ����Ҳ��֮Ϊcmos���ء����÷�����:

cmos c1(����ź�,�����ź�,TN�ܿ����ź�,TP�ܿ����ź�);

ͨ��TN�ܿ����źź�TP�ܿ����źű˴��ǻ�����,��TN�ܿ����ź�Ϊ1,Tp�ܿ����ź�Ϊ0ʱ,CMOs���ص�ͨ;���TN�ܿ����ź�Ϊ0,TP�ܿ����ź�Ϊ1ʱ,CMOs���ص�������ֳ����迹ֵz��CMOs���صĵ�Դ�͵�ͨ����MOS�ܵijĵ�����,�ʵ���cmosԪ��ʱ,����Ҫ���ǵ�Դ��ص��������⡣������c1����ʡ�ԡ�

�ؼ���rcmos�����˴�����Ԫ����һ��ģ��,��ĸr˵��������Ԫ��������˺������֮������ŵ���,���ź�ͨ��ʱ����ɷ���˥����ע��,Verilog�����ж�������ִ�����Ԫ���ź��ǵ������,��ǰ����ܵ�ʵ�ʴ�����Ԫ������һ�����졣

ͼ3.1.27��ʾ��·��Verilogģ������3.7.2��ʾ�������е�����һ�������ؼ��Զ�����²�ģ��inverter,�������Ϊv1(ע��,�����²�ģ��ʱ,����������ʡ��),��ɷ���Ĺ��ܡ�������������cmos����Ԫ��,������Veril-og���õĻ���Ԫ��,�ʵ�������ʡ�ԡ�

��3.7,2

//2-to-1 1multiplexer with CMOs switchs Fig.3.1.27

mlodule mymux2to1(X,Y,C,L);

input X, Y, c;

output L;

wire Cnot;

///instantiate inverter

invener v1(Cn��t,C);

//instantiate clrlos switch

c1mos(L,X,Cn��t,C);//(output,input,ncontrol,pcontro1)

cmos(L,Y,C,Cnot);

endmodule

//CMOs inverter Fig.3.1.8

module inverter(Vo,��i);

input Vi;

output Vo;

supply1Vdd;

supplyO GND;

pmos(��o,Vdd,��i); //(©��,Դ��,����դ��)

nm.os(��o,GND,Vi);

endnnodule

RNCF0805BTE215RVerilog�������ùؼ���cm��s�����˻���������Ԫ��ģ��,����һ������ˡ�һ�����˶˺��������ƶ�,��ͼ3.1.26��ʾ,ϰ����Ҳ��֮Ϊcmos���ء����÷�����:

cmos c1(����ź�,�����ź�,TN�ܿ����ź�,TP�ܿ����ź�);

ͨ��TN�ܿ����źź�TP�ܿ����źű˴��ǻ�����,��TN�ܿ����ź�Ϊ1,Tp�ܿ����ź�Ϊ0ʱ,CMOs���ص�ͨ;���TN�ܿ����ź�Ϊ0,TP�ܿ����ź�Ϊ1ʱ,CMOs���ص�������ֳ����迹ֵz��CMOs���صĵ�Դ�͵�ͨ����MOS�ܵijĵ�����,�ʵ���cmosԪ��ʱ,����Ҫ���ǵ�Դ��ص��������⡣������c1����ʡ�ԡ�

�ؼ���rcmos�����˴�����Ԫ����һ��ģ��,��ĸr˵��������Ԫ��������˺������֮������ŵ���,���ź�ͨ��ʱ����ɷ���˥����ע��,Verilog�����ж�������ִ�����Ԫ���ź��ǵ������,��ǰ����ܵ�ʵ�ʴ�����Ԫ������һ�����졣

ͼ3.1.27��ʾ��·��Verilogģ������3.7.2��ʾ�������е�����һ�������ؼ��Զ�����²�ģ��inverter,�������Ϊv1(ע��,�����²�ģ��ʱ,����������ʡ��),��ɷ���Ĺ��ܡ�������������cmos����Ԫ��,������Veril-og���õĻ���Ԫ��,�ʵ�������ʡ�ԡ�

��3.7,2

//2-to-1 1multiplexer with CMOs switchs Fig.3.1.27

mlodule mymux2to1(X,Y,C,L);

input X, Y, c;

output L;

wire Cnot;

///instantiate inverter

invener v1(Cn��t,C);

//instantiate clrlos switch

c1mos(L,X,Cn��t,C);//(output,input,ncontrol,pcontro1)

cmos(L,Y,C,Cnot);

endmodule

//CMOs inverter Fig.3.1.8

module inverter(Vo,��i);

input Vi;

output Vo;

supply1Vdd;

supplyO GND;

pmos(��o,Vdd,��i); //(©��,Դ��,����դ��)

nm.os(��o,GND,Vi);

endnnodule

�������

�������

- �غ�������ͨ��·���ıȽ�

- ������Դ��������Դ�ɵ������ؿ���

- ��·���������ͬ

- �ֶ�����10k��������Զ���ϵͳ����һ���ܻ�

- �غ������ѹһʱ���ͷֶ������

- ����FTU��ͨ�������Զ�����Ʒ���

- ֱ�������ͽ�������

- FQP34N20�¶���ʱ���·

- ���35k�������ϵ�ѹ�ȼ����վ�Ĺ涨

- SG2813J/883B 6��-64��������

�Ƽ���������

�Ƽ���������

- ��ѩ��������

- ������һ��dz���Ȥ��ͬʱ����һ�������Ѷȵ��淨��EDE2116AB... [��ϸ]

- ��һ������8ϵ���콢оƬӦ���о�

- ��Դ��ͨ�˲���(RC4558DN)Ӧ�����

- WTC6216����ʽ�������Ӧ

- ��Ƕ��ʽ�洢��ASIC��SoC����ص�����

- 16V��8A Silent Switcher

- ����ƥ���˲�оƬ

- ��ý��Э������SM501��Ƕ��ʽϵͳ�е�Ӧ��

- ����IEEE802.11b��EPA�¶ȱ�����

- QUICCEngine�������ƶ�IP�������

- SoC���������IJ�ҵ����

- MPC8xxϵ�д�������Ƕ��ʽϵͳ��Դ���

- dsPIC�����ڽ�����Ƶ�����е�Ӧ���о�

��������44030402000607

��������44030402000607