这个压降ΔU会对ADC产生什么样的影响呢

发布时间:2017/6/14 21:32:05 访问次数:580

这个压降ΔU会对ADC产生什么样的影响呢?也许会有人认为ADC中数字电路和模拟电路是两个相互隔离的电路,而且电平互不参考。 MAX724CCK实际上,数字电路与模拟电路之间寄生电容及磁珠的存在,已使两部分电路相互关联,因此Δσ的产生必然对ADC的正常工作产生影响。测试中发现,将ADC两边的数字地和模拟地用导线单点互连,可以通过±6kⅤ的静电放电测试。这是因为单点互连后Δσ大大降低。

ADC数字地与模拟地之间用磁珠连接是I程师在电路设计中经常发生的错误,这些错误首先来自ADC电源引脚和接地引脚的名称。模拟地和数字地的引脚名称表示内部元件本身的作用,但是未必意味着外部也应该按照内部作用去做。ADC集成电路内部有模拟电路和数字电路两部分,为了避免数字信号耦合到模拟电路中去,模拟地和数字地通常分开,如图2.91所示的ADC。但是从芯片上的焊点到封装引脚的连线所产生的引线接合电感和电阻,并不是℃设计者专门加上去的。快速变化的数字电流在B点产生一个电压,经过寄生

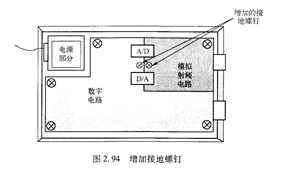

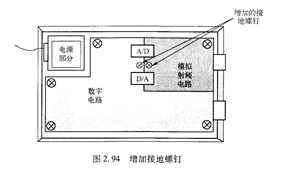

电容必然耦合到模拟电路的A点。可见,在数字地与模拟地之间串联磁珠并不能减小数字电路的噪声向模拟电路传输,而且任何在数字地引脚附加的外部阻抗都将在B点上引起较大的数字噪声,然后,大的数字噪声通过杂散电容耦合到模拟电路上。芯片内部杂散电容产生的耦合是制造芯片过程中IC设计者应考虑的问题。为了防止进一步耦合,需要模拟地和数字地的引脚在外面用最短的连线接到同一个低阻抗的接地平面上。本案例中金属外壳的底板实际上提供一个低阻抗的接地平面,但PCB与金属底板的连接点离ADC太远,高频下,对于ADC的两个地引脚来讲,并不能实现低阻抗接地。如果再在ADC附近增加两个接地点,一个在模拟电路侧,另一个在数字电路侧,如图2.%所示,将大大增强接地效果。

这个压降ΔU会对ADC产生什么样的影响呢?也许会有人认为ADC中数字电路和模拟电路是两个相互隔离的电路,而且电平互不参考。 MAX724CCK实际上,数字电路与模拟电路之间寄生电容及磁珠的存在,已使两部分电路相互关联,因此Δσ的产生必然对ADC的正常工作产生影响。测试中发现,将ADC两边的数字地和模拟地用导线单点互连,可以通过±6kⅤ的静电放电测试。这是因为单点互连后Δσ大大降低。

ADC数字地与模拟地之间用磁珠连接是I程师在电路设计中经常发生的错误,这些错误首先来自ADC电源引脚和接地引脚的名称。模拟地和数字地的引脚名称表示内部元件本身的作用,但是未必意味着外部也应该按照内部作用去做。ADC集成电路内部有模拟电路和数字电路两部分,为了避免数字信号耦合到模拟电路中去,模拟地和数字地通常分开,如图2.91所示的ADC。但是从芯片上的焊点到封装引脚的连线所产生的引线接合电感和电阻,并不是℃设计者专门加上去的。快速变化的数字电流在B点产生一个电压,经过寄生

电容必然耦合到模拟电路的A点。可见,在数字地与模拟地之间串联磁珠并不能减小数字电路的噪声向模拟电路传输,而且任何在数字地引脚附加的外部阻抗都将在B点上引起较大的数字噪声,然后,大的数字噪声通过杂散电容耦合到模拟电路上。芯片内部杂散电容产生的耦合是制造芯片过程中IC设计者应考虑的问题。为了防止进一步耦合,需要模拟地和数字地的引脚在外面用最短的连线接到同一个低阻抗的接地平面上。本案例中金属外壳的底板实际上提供一个低阻抗的接地平面,但PCB与金属底板的连接点离ADC太远,高频下,对于ADC的两个地引脚来讲,并不能实现低阻抗接地。如果再在ADC附近增加两个接地点,一个在模拟电路侧,另一个在数字电路侧,如图2.%所示,将大大增强接地效果。

上一篇:碳膜电阻体会因电流过大而严重烧坏

上一篇:按照以上的分析及测试结果

公网安备44030402000607

公网安备44030402000607