集成计数器的设计(设计性实验)

发布时间:2012/9/15 12:52:57 访问次数:1535

集成计数器Q12P1CXXY24E的设计(设计性实验)

1.实验目的

(1)学习用集成触发器构成计数器的方法。

(2)掌握中规模集成计数器的使用及功能测试。

(3)运用集成计数器构成任意进制计数器。

2.实验设备与器材

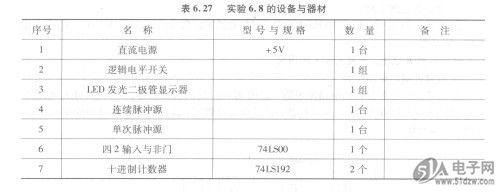

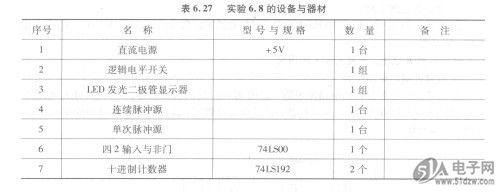

实验所用设备与器材见表6.27。

3.设计提示与要求

1)设计提示

①中规模十进制计数器74LS192

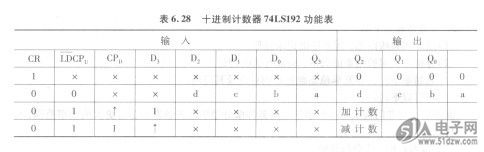

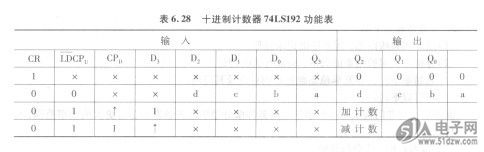

74LS192是同步十进制可逆计数器,具有双时钟输入,并具有清零和置数等功能,其引脚排列及逻辑符号如图6. 33所示。其中,LD为置数端;CPu为加计数端;CPD为减计数端;CO为非同步进位输出端;BO为非同步借位输出端;Do、D1、D2、D3为计数器输入端;Qo、Q1、Q2、Q3为数据输出端;CR为清零端。74LSJ92逻辑功能表如表6.28所示。

集成计数器Q12P1CXXY24E的设计(设计性实验)

1.实验目的

(1)学习用集成触发器构成计数器的方法。

(2)掌握中规模集成计数器的使用及功能测试。

(3)运用集成计数器构成任意进制计数器。

2.实验设备与器材

实验所用设备与器材见表6.27。

3.设计提示与要求

1)设计提示

①中规模十进制计数器74LS192

74LS192是同步十进制可逆计数器,具有双时钟输入,并具有清零和置数等功能,其引脚排列及逻辑符号如图6. 33所示。其中,LD为置数端;CPu为加计数端;CPD为减计数端;CO为非同步进位输出端;BO为非同步借位输出端;Do、D1、D2、D3为计数器输入端;Qo、Q1、Q2、Q3为数据输出端;CR为清零端。74LSJ92逻辑功能表如表6.28所示。

热门点击

热门点击

- 三相异步电动机启停的PLC控制

- 简单的方波一三角波产生电路

- 直插式元器件引脚处理

- 兆欧表的工作原理

- 环形多谐振荡器

- 正负误差补偿法

- 交流电路的戴维南等效电路(综合性实验)

- 测量三极管集电结反向电阻

- 指针万用表的性能指标

- FET与晶体管混合的达林顿连接

推荐技术资料

推荐技术资料

- 单片机版光立方的制作

- N视频: http://v.youku.comN_sh... [详细]

公网安备44030402000607

公网安备44030402000607