降低寄生双极管的pPNP和pNPN值

发布时间:2012/4/23 19:41:15 访问次数:10241

pPNP×pNPN>l是引起CMOS电路中寄LP3972SQ-A514生晶闸管触发的基本条件。在加工工艺和版图设计中可以采取如下的措施来降低寄生双极管的pPNP和pNPN:

①N阱或P阱要保证有足够的深度。在数字CMOS电路中阱不能按比例缩小,阱深仍然要保持在3~4Ym,亚微米电路也要保证在2~3pm。阱深越深越好,有利于抑制晶闸管效应。

②BiCMOS电路中,对于N阱,BiCMOS电路N阱底下要加有N埋;对于P阱BiCMOS电路中P管区底下要加有N埋,P阱底下加有P埋。

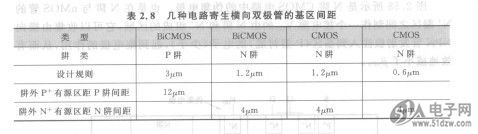

③为了降诋横向双极管的pPN,(或pNPN)值,P阱CMOS中PMOS管源漏P+离P阱边缘的间距,以及N阱CMOS中NMOS管源漏N+离N阱边缘的间距要尽可能远些。表2.8给出了几种电路寄生横向双极管的间距(即基区宽度)。

④因输出级驱动电流较大,故输出级的PMOS和NMOS管通常都一定要设法设计在压焊块的两侧,拉大寄生横向双极管的距离。

pPNP×pNPN>l是引起CMOS电路中寄LP3972SQ-A514生晶闸管触发的基本条件。在加工工艺和版图设计中可以采取如下的措施来降低寄生双极管的pPNP和pNPN:

①N阱或P阱要保证有足够的深度。在数字CMOS电路中阱不能按比例缩小,阱深仍然要保持在3~4Ym,亚微米电路也要保证在2~3pm。阱深越深越好,有利于抑制晶闸管效应。

②BiCMOS电路中,对于N阱,BiCMOS电路N阱底下要加有N埋;对于P阱BiCMOS电路中P管区底下要加有N埋,P阱底下加有P埋。

③为了降诋横向双极管的pPN,(或pNPN)值,P阱CMOS中PMOS管源漏P+离P阱边缘的间距,以及N阱CMOS中NMOS管源漏N+离N阱边缘的间距要尽可能远些。表2.8给出了几种电路寄生横向双极管的间距(即基区宽度)。

④因输出级驱动电流较大,故输出级的PMOS和NMOS管通常都一定要设法设计在压焊块的两侧,拉大寄生横向双极管的距离。

上一篇:防止晶闸管(闭锁)效应的措施

上一篇:少数载流子的保护环

公网安备44030402000607

公网安备44030402000607