CMOS或非门

发布时间:2012/2/14 21:26:05 访问次数:3304

CMOS或非门PVG610X

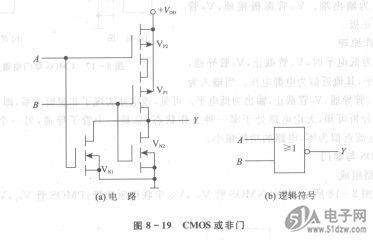

(1)电路组成

电路如图8 -19所示,其中VN1,VN2为NMOS驱动管;VP1,VP2为PMOS负载管。

(2)工作原理

当A=O,B=O时,VN1,VN2截止,VP1,VP2导通,输出Y=l。

当A =0,B=l时,VN2截止,VP1导通,输出Y=O。

当A=l,B=O时,VN1截止,VP2导通,输出Y=O。

当A=l,B=l时,VN1,VN2导通,VP1,VP2截止,输出Y=O。

可见,该电路实现了或菲逻辑关系,即Y=A+B。

CMOS三态门

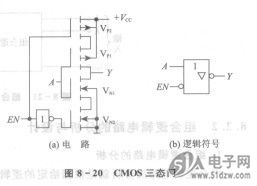

(1)电路组成

图8 - 20为CMOS三态门的电路图和逻辑符号。A为信号输入端,EN为三态控制端。图中VN1,VP1构成反向器,VN2,VP2作为控制开关。

(2)工作原理

当EN输入端为低电平时均导通,输入/输出之间实现非门功能,即当A=O时,Y=l;A=l时,Y=O。

当EN输入端为高电平时,VN2,VP2均截止,无论A=l或O,输出y均为高阻状态。

CMOS或非门PVG610X

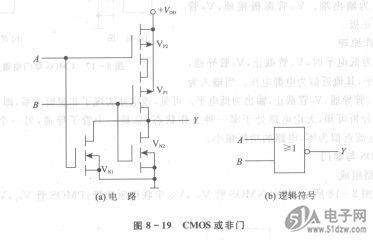

(1)电路组成

电路如图8 -19所示,其中VN1,VN2为NMOS驱动管;VP1,VP2为PMOS负载管。

(2)工作原理

当A=O,B=O时,VN1,VN2截止,VP1,VP2导通,输出Y=l。

当A =0,B=l时,VN2截止,VP1导通,输出Y=O。

当A=l,B=O时,VN1截止,VP2导通,输出Y=O。

当A=l,B=l时,VN1,VN2导通,VP1,VP2截止,输出Y=O。

可见,该电路实现了或菲逻辑关系,即Y=A+B。

CMOS三态门

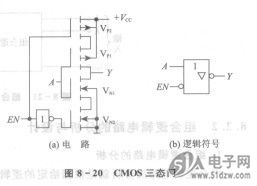

(1)电路组成

图8 - 20为CMOS三态门的电路图和逻辑符号。A为信号输入端,EN为三态控制端。图中VN1,VP1构成反向器,VN2,VP2作为控制开关。

(2)工作原理

当EN输入端为低电平时均导通,输入/输出之间实现非门功能,即当A=O时,Y=l;A=l时,Y=O。

当EN输入端为高电平时,VN2,VP2均截止,无论A=l或O,输出y均为高阻状态。

上一篇:CMOS集成门电路

上一篇:MOS集成电路使用注意事项

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607