HyperLynx FAST 3D场解析器封装和PCB集成

发布时间:2020/12/4 23:58:56 访问次数:1303

HS4x处理器提供单核、双核和四核配置,速度最高可达到每集群24,000 DMIPS。HS46和HS48提供指令和数据缓存(每个缓存高达64 KB),完全支持一级(L1)缓存一致性。

Siemens 业务部门 Mentor 今天宣布推出业内最全面和高效的针对先进 IC 封装设计的解决方案 ― Xpedition® 高密度先进封装 (HDAP) 流程。这一全面的端到端解决方案结合了 Mentor® Xpedition、HyperLynx® 和 Calibre® 技术,实现了快速的样机制作和 GDS Signoff。

HDAP 方法和技术,全新 Mentor IC 封装设计流程提供了更快速、更优质的结果。

FOWLP 在 2015 年至 2020 年内的增长率将达到惊人的 82%,FOWLP 会干扰传统的设计和制造供应链。与其他高密度先进封装技术一样,它将推动对设备与封装协同设计以及新流程的需求,如 Mentor HDAP 解决方案。

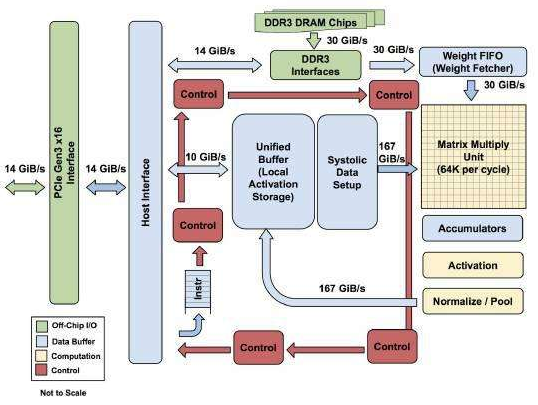

独一无二的 HDAP 集成、样机制作和封装设计技术,新的 HDAP 流程引入了两项独特的技术。第一个是 Xpedition Substrate Integrator 工具,它是一个图形化、快速的虚拟原型设计环境,能够探索异构 IC 并将其与中介层、封装和 PCB 集成。

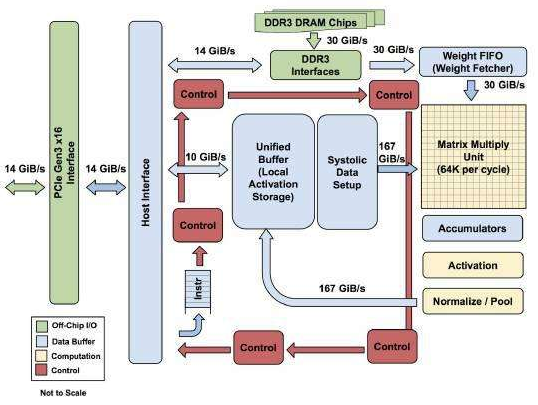

封装设计师可使用 HyperLynx FAST 3D 场解析器进行提取和分析,进行 SI/PI 3D 模型仿真。HyperLynx DRC 工具可轻松识别和解决基底级别的 DRC 错误,通常能够在最终流片和 Signoff 验证之前发现 80%-90% 的问题。

Calibre® 3DSTACK 技术与 Xpedition Package Designer 工具集成之后,Calibre 3DSTACK 技术可提供 2.5D/3D 封装物理验证。IC 封装设计师可以在任何工艺节点对整个多芯片系统进行设计规则检查 (DRC) 和布局与原理图 (LVS) 检查,而无需破坏现有工具流程或要求新的数据格式,从而极大地减少了流片时间。

(素材来源:21IC.如涉版权请联系删除。特别感谢)

HS4x处理器提供单核、双核和四核配置,速度最高可达到每集群24,000 DMIPS。HS46和HS48提供指令和数据缓存(每个缓存高达64 KB),完全支持一级(L1)缓存一致性。

Siemens 业务部门 Mentor 今天宣布推出业内最全面和高效的针对先进 IC 封装设计的解决方案 ― Xpedition® 高密度先进封装 (HDAP) 流程。这一全面的端到端解决方案结合了 Mentor® Xpedition、HyperLynx® 和 Calibre® 技术,实现了快速的样机制作和 GDS Signoff。

HDAP 方法和技术,全新 Mentor IC 封装设计流程提供了更快速、更优质的结果。

FOWLP 在 2015 年至 2020 年内的增长率将达到惊人的 82%,FOWLP 会干扰传统的设计和制造供应链。与其他高密度先进封装技术一样,它将推动对设备与封装协同设计以及新流程的需求,如 Mentor HDAP 解决方案。

独一无二的 HDAP 集成、样机制作和封装设计技术,新的 HDAP 流程引入了两项独特的技术。第一个是 Xpedition Substrate Integrator 工具,它是一个图形化、快速的虚拟原型设计环境,能够探索异构 IC 并将其与中介层、封装和 PCB 集成。

封装设计师可使用 HyperLynx FAST 3D 场解析器进行提取和分析,进行 SI/PI 3D 模型仿真。HyperLynx DRC 工具可轻松识别和解决基底级别的 DRC 错误,通常能够在最终流片和 Signoff 验证之前发现 80%-90% 的问题。

Calibre® 3DSTACK 技术与 Xpedition Package Designer 工具集成之后,Calibre 3DSTACK 技术可提供 2.5D/3D 封装物理验证。IC 封装设计师可以在任何工艺节点对整个多芯片系统进行设计规则检查 (DRC) 和布局与原理图 (LVS) 检查,而无需破坏现有工具流程或要求新的数据格式,从而极大地减少了流片时间。

(素材来源:21IC.如涉版权请联系删除。特别感谢)

公网安备44030402000607

公网安备44030402000607