���е��Զ��ָ��Ͷϵ�ʱ�IJ��д����������

����ʱ��:2020/6/8 13:28:49 ���ʴ���:2276

GBDriver RS2��ʵ���˸��ٿ��Ƶ�ͬʱ���߱���������15bit ECC�������룩��ǿ�����У�鹦�ܣ��Լ�TDK GBDriverϵ�й��е��Զ��ָ����ܣ������ŶԿ������ϵ�ʱ�IJ��д���������ܣ������NAND��������ݿɿ��ԡ�

GBDriver RA2ϵ�в�����һ�ֶ����ľ�̬����ƽ���㷨 (Static Wear Leveling Algorithm)��ʹÿ���洢��IJ�д��������ƽ��������������ȵ��ӳ���NAND����IJ�д������SMART�����Ҽ�⡢�����ͱ��漼��������ȷ����ÿ���洢��IJ�д������ʹ��������������������ӱ�����

������������ʹ��AES 128bit2�����㷨���Զ����ܹ��ܡ�ͨ������NAND�����е��������������ݴܸĺ�й¶���ṩ��ǿ��İ�ȫ��������GBDriver RS2�������Ĺ�ҵSATA II��̬Ӳ��(SSD)��

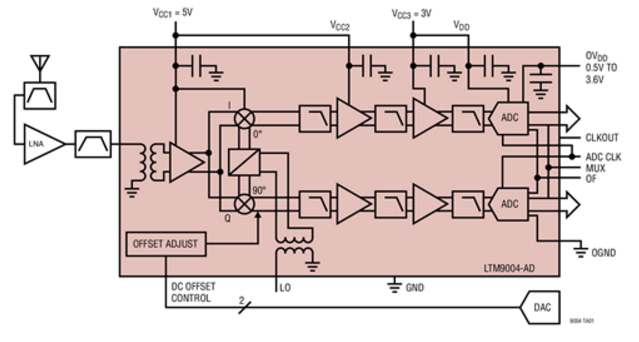

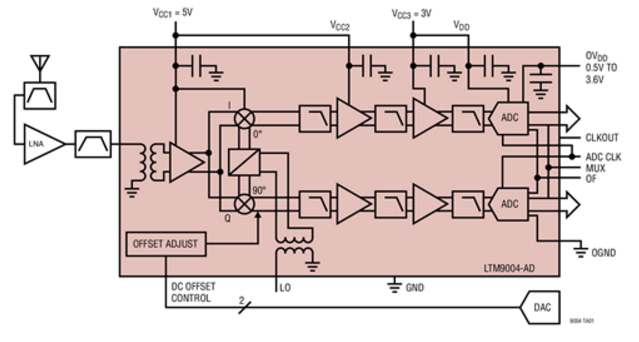

������ 14 λ��150Msps ģ��ת���� (ADC) LTC2262������ 149mW ���ʣ������ͬ�����������ĵ� 1/3�������µĻ�ʹ����Щ�������ϸ���Ԥ��ı�ЯʽӦ���ܹ���չ�����ܣ���Ϊ 3G/4G LTE �� WiMAX ��վ�豸�ṩ�ϸߵĹ���Ч�ʺͼ��;����������ɱ����������ĵ͵ö�Ĺ��ʣ�LTC2262 �����������ֶ��صĹ��ܣ������������õIJ�������Ҳ����ʧЧ������¼������ַ�������Щ�ص��֮���ʿɼ����ڶ���Ӧ���в��ø��� ADC ����������ĸ�������ЩӦ�ð�����Яʽҽ�Ƴ���ͳ�������Яʽ���Ժ��DZ������ƻ��Բ����豸��������������ߵ�ͷ��ѻ�վ��

������ADC������������������ģ�ⲿ��ʱ���������ַ������Ӷ���������ã������������б���Ϊ�����״������ADC���Ƶ���������Ϊ��ɢ����������������������б�ȴ�������������������� 1 ��Ϊ 0����� 0 ��Ϊ 1���Ӷ����������ϻ�����ĵص�����

LTC2262 �Ĵ��������������������Ϊ������ CMOS��˫�������� CMOS ��˫�������� LVDS��˫�������������������������ʱ�ӵ������غ��½��ط��ͣ��Ӷ�����������������������һ�롣һ�������������Դ���� CMOS ����� 1.2V �� 1.8V �ķ�Χ�ڰڶ���

LTC2262 ���� 6mm x 6mm QFN ��װ������һ������ʹ�÷� 50% ʱ��ռ�ձȵ�ʱ��ռ�ձ��ȶ�����·���ɱ�����������ʱ���ɱ�� LVDS ��������Լ���ѡ LVDS ����նˡ���Щ�ص������ʹ ADC �����ֽ�����֮������ݴ���������ˡ�

LTC2262 ����һ�����ż��ݵ� 14 λ�� 12 λ ADC ϵ�У����ϵ�е������ֱ���� 25Msps �� 150Msps �IJ����ʺ� 35mW �� 149mW �Ĺ��ġ�

(�ز���Դ��21IC��ttic��eechina.�����Ȩ����ϵɾ�����ر��л��

���������ط�Ƽ�����˾http://ytf01.51dzw.com/

GBDriver RS2��ʵ���˸��ٿ��Ƶ�ͬʱ���߱���������15bit ECC�������룩��ǿ�����У�鹦�ܣ��Լ�TDK GBDriverϵ�й��е��Զ��ָ����ܣ������ŶԿ������ϵ�ʱ�IJ��д���������ܣ������NAND��������ݿɿ��ԡ�

GBDriver RA2ϵ�в�����һ�ֶ����ľ�̬����ƽ���㷨 (Static Wear Leveling Algorithm)��ʹÿ���洢��IJ�д��������ƽ��������������ȵ��ӳ���NAND����IJ�д������SMART�����Ҽ�⡢�����ͱ��漼��������ȷ����ÿ���洢��IJ�д������ʹ��������������������ӱ�����

������������ʹ��AES 128bit2�����㷨���Զ����ܹ��ܡ�ͨ������NAND�����е��������������ݴܸĺ�й¶���ṩ��ǿ��İ�ȫ��������GBDriver RS2�������Ĺ�ҵSATA II��̬Ӳ��(SSD)��

������ 14 λ��150Msps ģ��ת���� (ADC) LTC2262������ 149mW ���ʣ������ͬ�����������ĵ� 1/3�������µĻ�ʹ����Щ�������ϸ���Ԥ��ı�ЯʽӦ���ܹ���չ�����ܣ���Ϊ 3G/4G LTE �� WiMAX ��վ�豸�ṩ�ϸߵĹ���Ч�ʺͼ��;����������ɱ����������ĵ͵ö�Ĺ��ʣ�LTC2262 �����������ֶ��صĹ��ܣ������������õIJ�������Ҳ����ʧЧ������¼������ַ�������Щ�ص��֮���ʿɼ����ڶ���Ӧ���в��ø��� ADC ����������ĸ�������ЩӦ�ð�����Яʽҽ�Ƴ���ͳ�������Яʽ���Ժ��DZ������ƻ��Բ����豸��������������ߵ�ͷ��ѻ�վ��

������ADC������������������ģ�ⲿ��ʱ���������ַ������Ӷ���������ã������������б���Ϊ�����״������ADC���Ƶ���������Ϊ��ɢ����������������������б�ȴ�������������������� 1 ��Ϊ 0����� 0 ��Ϊ 1���Ӷ����������ϻ�����ĵص�����

LTC2262 �Ĵ��������������������Ϊ������ CMOS��˫�������� CMOS ��˫�������� LVDS��˫�������������������������ʱ�ӵ������غ��½��ط��ͣ��Ӷ�����������������������һ�롣һ�������������Դ���� CMOS ����� 1.2V �� 1.8V �ķ�Χ�ڰڶ���

LTC2262 ���� 6mm x 6mm QFN ��װ������һ������ʹ�÷� 50% ʱ��ռ�ձȵ�ʱ��ռ�ձ��ȶ�����·���ɱ�����������ʱ���ɱ�� LVDS ��������Լ���ѡ LVDS ����նˡ���Щ�ص������ʹ ADC �����ֽ�����֮������ݴ���������ˡ�

LTC2262 ����һ�����ż��ݵ� 14 λ�� 12 λ ADC ϵ�У����ϵ�е������ֱ���� 25Msps �� 150Msps �IJ����ʺ� 35mW �� 149mW �Ĺ��ġ�

(�ز���Դ��21IC��ttic��eechina.�����Ȩ����ϵɾ�����ر��л��

���������ط�Ƽ�����˾http://ytf01.51dzw.com/

��һƪ������λ����ģʽ������λ���е���

��һƪ���͵�ͨ������͵Ĵ������

�������

�������

- ��ģ�˲���ģ�˲���·

- ���������������

- �����뵼�����ݰ�Ŀ��ģ��

- �����豸�������߶��Ż�

- I/O�ӿڼ��߿ɿ������ݴ���

- ��Ʒ��©Դ��ͨ���轵��

- ���������Եĸ���ƽ���Ȳ�

- ��Դ��λ������������������

- ����˫SPI�������������е��������ߵ���

- ��ϵͳ�е�RF���ʲ���

�Ƽ���������

�Ƽ���������

- �й���ý��ѧ��ý����ݿ�

- ��ý����ݿ�����ʽ¡ͯ���С�������i���ҹ���ֵܾȲ���... [��ϸ]

��������44030402000607

��������44030402000607