S1008R-152K 存储器、复杂可编程器件

发布时间:2019/10/24 17:39:03 访问次数:530

S1008R-152K电路为两个555定时器构成的频率可调而脉宽不变的方波发生器,试说明工作原理;确定频率变化的范围和输出脉宽;解释二极管D在电路中的作用。

D/A转换器的基本原理

D/A转换器的框图如图9.1.1所示.图中,输入数字量NB为n位二进制代码DN-1DN-2...D1D0,U0(或io)为输出模拟量,输出量与输入量之间的一般关系式为

Dn~1Dn~2・・・DlDO9

输出量与输人量之间的一般关系式为

Di2I (9.1.1)・

Jo(或Jo)=Κ∑

式中比例系数Κ是一个常数.

任何一个二进制数DN-1DN-2...D1D0可以按下式转换为(MSB)方框图图9.1.1 D/A转换器

(Ⅳ):=Dr1×2卜1+D汔~2×2

式中2n~1、2^2、…、21、2°为各数位

换的过程,是将输人成模这些模拟转换器求和电路可以按下式转换为十进制数

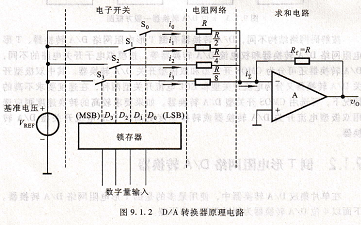

数字量输入图9.1.2 D/A转换器原理电路9.1 D偌换器D/A电子开关电阻网络基准电压+D1锁存器.

为实现上述过程,FGPA中都设有相应的引脚,主要包括编程使能、数据输入、数据输出、状态指示、时钟等信号。表7.4.4所示为Spadan-Ⅱ、spartan-ⅡE、Virtex、Ⅴi1・tex-E系列FPGA芯片用于装载配置数据的相关引脚说明。

表7.4.4 FPGA中用于装载配置数据的相关引脚

当在FPGA的三个专用引脚M2、M1和M0上输人不同的逻辑电平时,便可选择一种配置模式进行数据装人。配置模式如表7.4.5所示。主模式利用FPGA内部振荡器产生配置时钟信号CCLK来驱动装有编程数据的PROM。而从模式则需要外部电路提供时钟信号来驱动CCLK和装有编程数据的PROM。

存储器、复杂可编程器件和切场可编程阵列MO, M1, M2用于指定配置模式CCLK配置时钟的输入/输出引脚。当采用从配置模式时为输人,采用主配置模式时为输出。配置完成后为输人方式,但处于无关逻辑电平PROGRAM低电平时开始配置过程DONE由低到高时表示配置装载完成。

输人低电平时可以推迟启动工作。输出可以为漏极开路方式为低电平时表示配置存储单元正在清零,配置结束后可作为用户1/o在从并模式下,BUSY控制配置数据的装载速率。在串行模式下,多个器件采用链式配置时,DOUT作为向下一级传递数据流的出口。配置完成后可作为用户的I/0DO/DIN, D1,D2, D3, D4,

D5, D6, D7在从并模式下,DO~D7为配置数据输人端。在串行模式下,DIN为串行数据输人端。配置完成后都可作为用户的I/o在从并模式下,写使能信号,低电平有效。配置完成后可作为用户的I/o在从并模式下,片选信号,低电平有效。配置完成后可作为用户的I/oVcc NT内部核心逻辑电源引脚输出驱动电源引脚INIT BUSY/DOUTCs是否专用.

当选择串行模式时,编程数据从PROM中以串行方式装人FPGA中,此时必须用有串行功能的PROM。主串装人模式电路如图7.4.12所示。当选择并行模式时,除了时钟信号外,还需提供其他读写控制信号。

FPGA不仅能够直接从PROM中读取配置数或单片机控制装入配置数据。近年来,随着半导体工艺的进一步提高,,而且可以由其他微处理器FPGA的发展速度也相当快。

Xilinx公司的早期产品XC2000、XC3000系列已经淘汰,XC4000系列也已进入淘汰行列。淘汰的主要原因是受当时工艺所限,密度较低,单位逻辑单元的成本较高,且使用的工作电压较高,功耗大。另外就是I/0接口的适应性差,无法满足目前低电压系统工作的要求。目前,两个新型系列Spartan和Virtex已经取代了早期产品。Spartan系列属于高密度低价FPGA,其中Spartan-Ⅱ(2.5V核心工作电压)和Spartan-ⅡE(1.8V核心工作电压)已成为主流产品,可适应5V、3.3Ⅴ、2.5V、1.8V、1,5Ⅴ等电源系统下的I/0接口。

S1008R-152K电路为两个555定时器构成的频率可调而脉宽不变的方波发生器,试说明工作原理;确定频率变化的范围和输出脉宽;解释二极管D在电路中的作用。

D/A转换器的基本原理

D/A转换器的框图如图9.1.1所示.图中,输入数字量NB为n位二进制代码DN-1DN-2...D1D0,U0(或io)为输出模拟量,输出量与输入量之间的一般关系式为

Dn~1Dn~2・・・DlDO9

输出量与输人量之间的一般关系式为

Di2I (9.1.1)・

Jo(或Jo)=Κ∑

式中比例系数Κ是一个常数.

任何一个二进制数DN-1DN-2...D1D0可以按下式转换为(MSB)方框图图9.1.1 D/A转换器

(Ⅳ):=Dr1×2卜1+D汔~2×2

式中2n~1、2^2、…、21、2°为各数位

换的过程,是将输人成模这些模拟转换器求和电路可以按下式转换为十进制数

数字量输入图9.1.2 D/A转换器原理电路9.1 D偌换器D/A电子开关电阻网络基准电压+D1锁存器.

为实现上述过程,FGPA中都设有相应的引脚,主要包括编程使能、数据输入、数据输出、状态指示、时钟等信号。表7.4.4所示为Spadan-Ⅱ、spartan-ⅡE、Virtex、Ⅴi1・tex-E系列FPGA芯片用于装载配置数据的相关引脚说明。

表7.4.4 FPGA中用于装载配置数据的相关引脚

当在FPGA的三个专用引脚M2、M1和M0上输人不同的逻辑电平时,便可选择一种配置模式进行数据装人。配置模式如表7.4.5所示。主模式利用FPGA内部振荡器产生配置时钟信号CCLK来驱动装有编程数据的PROM。而从模式则需要外部电路提供时钟信号来驱动CCLK和装有编程数据的PROM。

存储器、复杂可编程器件和切场可编程阵列MO, M1, M2用于指定配置模式CCLK配置时钟的输入/输出引脚。当采用从配置模式时为输人,采用主配置模式时为输出。配置完成后为输人方式,但处于无关逻辑电平PROGRAM低电平时开始配置过程DONE由低到高时表示配置装载完成。

输人低电平时可以推迟启动工作。输出可以为漏极开路方式为低电平时表示配置存储单元正在清零,配置结束后可作为用户1/o在从并模式下,BUSY控制配置数据的装载速率。在串行模式下,多个器件采用链式配置时,DOUT作为向下一级传递数据流的出口。配置完成后可作为用户的I/0DO/DIN, D1,D2, D3, D4,

D5, D6, D7在从并模式下,DO~D7为配置数据输人端。在串行模式下,DIN为串行数据输人端。配置完成后都可作为用户的I/o在从并模式下,写使能信号,低电平有效。配置完成后可作为用户的I/o在从并模式下,片选信号,低电平有效。配置完成后可作为用户的I/oVcc NT内部核心逻辑电源引脚输出驱动电源引脚INIT BUSY/DOUTCs是否专用.

当选择串行模式时,编程数据从PROM中以串行方式装人FPGA中,此时必须用有串行功能的PROM。主串装人模式电路如图7.4.12所示。当选择并行模式时,除了时钟信号外,还需提供其他读写控制信号。

FPGA不仅能够直接从PROM中读取配置数或单片机控制装入配置数据。近年来,随着半导体工艺的进一步提高,,而且可以由其他微处理器FPGA的发展速度也相当快。

Xilinx公司的早期产品XC2000、XC3000系列已经淘汰,XC4000系列也已进入淘汰行列。淘汰的主要原因是受当时工艺所限,密度较低,单位逻辑单元的成本较高,且使用的工作电压较高,功耗大。另外就是I/0接口的适应性差,无法满足目前低电压系统工作的要求。目前,两个新型系列Spartan和Virtex已经取代了早期产品。Spartan系列属于高密度低价FPGA,其中Spartan-Ⅱ(2.5V核心工作电压)和Spartan-ⅡE(1.8V核心工作电压)已成为主流产品,可适应5V、3.3Ⅴ、2.5V、1.8V、1,5Ⅴ等电源系统下的I/0接口。

公网安备44030402000607

公网安备44030402000607