ZMM2.4 倒T形电阻网络D/A转换器

发布时间:2019/10/24 17:39:55 访问次数:1428

ZMM2.4权电阻网络、求和电路、基准电压、锁存器等组成。

电子开关SO~S3分别由输入数码D0~D3控制,当D=1,si接通;当Di=0,si断开。权电阻网络与运算放大器A组成求和电路。根据线性运用条

件下,运放虚短、虚断的特点有

将它们代人式(9.1.2)则得

结果表明,电路实现了从数字量到模拟量的转换。

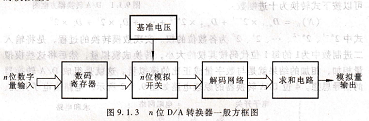

位D/A转换器的一般框图如图9.1.3所示。图中,数字量以串行或并行方式输人并存储于数码寄存器中,寄存器的输出驱动对应数位上的电子开关将相应数位的权值送入求和电路。求和电路将各位的权值相加得到与数字量对应的模拟量。

″位数字量输入位D/A转换器一般方框图

按解码网络结构不同,D/A转换器有倒T形电阻网络D/A转换器、T形电阻网络D/A转换器和权电流D/A转换器等。按模拟电子开关电路的不同,D/A转换器还可分为CMOs开关型和双极型开关D/A转换器。其中双极型开关D/A转换器又分为电流开关型和ECL电流开关型两种,在速度要求不高的情况下,可选用CMOS开关型D/A转换器。如果要求较高的转换速度则应选用双极型电流开关D/A转换器或转换速度更高的ECL电流开关型D/A转换器。

在单片集成D/A转换器中,使用最多的是倒T形电阻网络D/A转换器c下面以4位D/A转换器为例说明其工作原理。

Virtex系列为高密度、高性能产品。其中Ⅴirtex-E(1.8Ⅴ核心工作电压)和Virtex-Ⅱ(1.5V核心工作电压)也已逐渐成为主流产品。Ⅴirtex-Ⅱ内部时钟工作频率可达420 MHz,且内部已集成了18×18乘法器。表7.4,6所示为几种典型的FPGA产品规模。由表中看出,XC2Ⅴ8000最大可用引脚数已达1108个。

Xilinx公司几种典型的FPG实现逻辑功能元的组织方式公司外,Altera也是最大的可编程逻辑器件供应商之一,基本原理类似于Xilinx公司的FPGA。它们的主要区别和内部连接布线方式不同。Altera的FPGA中逻辑块所其FPGA是逻辑单包含的逻辑单元较多,一般为8个以上。内连方式采用纵横交错的快速互联通道(Fast~Track),没有用开关矩阵,信号的传输延时一致性较好。Altera FPGA的产品主要有FLEⅩ、APEX、straux、cyclone、MAXII等。其中FLEX和APEX属于20世纪90年代末的产品,目前逐渐被stratix和Cyclone取代。

spanan-Ⅱ系列的FPGA中,1个CLB有几个微中有几个LUT?

几个触发器?1个CLB能实现多少变量的任意逻辑函数?

可编程开关点(图7.3.4)和可编程开关矩阵中的连接点有何区别?

为什么在FPGA构成的数字系统中要配各一个PROM或EPROM?

FPGA与CPLD有哪些主要区别?它们各有什么特点?

设计一个定时器。要求:定时时间为24s,按递减方式计时,每隔1s,定时器减1。

设置两个外部控制开关(控制功能如表7.5.1所示),控制定时器的直接复位、启动计时、暂停/连续计时。

当定时器递减计时到零(即定时时间到)时,定时器保持零不变,同时发出报警信号。

输入时钟脉冲的频率为1 Hz,输出为8421表7.5.1 定时器功能表BCD码。

解:(1)逻辑设计,用计数器对1 Hz的时钟信号进行计数,其计数值即为定时时间。根据设计要求可知,电路需要输出2组8421BCD码,计数器初值为24,按递减方式计数,减到0时,输出报警信号,并能控制计数器暂停/连续计数,所以需要

设计一个可预置初值的带使能控制端的递减计数器。

实现上述功能的Verilog HDL程序如下。HDL描述分为3部分:第一部分定义了电路的输入、输出信号。其输入信号为复位nRsT(低电平有效)、暂停/连续nPAusE和时钟CP。输出信号为TimerH(定时器的十位)、TimerL(定时器的个位)和报警Alarm。第二部分用一个连续赋值语句assign说明当计数器递减到0时,输出报警信号(Alarm=1)。第三部分用一个过程块always说明计数器的计数、处理操作,计数器的个位和十位均按8421BCD码方式递减计数。

ZMM2.4权电阻网络、求和电路、基准电压、锁存器等组成。

电子开关SO~S3分别由输入数码D0~D3控制,当D=1,si接通;当Di=0,si断开。权电阻网络与运算放大器A组成求和电路。根据线性运用条

件下,运放虚短、虚断的特点有

将它们代人式(9.1.2)则得

结果表明,电路实现了从数字量到模拟量的转换。

位D/A转换器的一般框图如图9.1.3所示。图中,数字量以串行或并行方式输人并存储于数码寄存器中,寄存器的输出驱动对应数位上的电子开关将相应数位的权值送入求和电路。求和电路将各位的权值相加得到与数字量对应的模拟量。

″位数字量输入位D/A转换器一般方框图

按解码网络结构不同,D/A转换器有倒T形电阻网络D/A转换器、T形电阻网络D/A转换器和权电流D/A转换器等。按模拟电子开关电路的不同,D/A转换器还可分为CMOs开关型和双极型开关D/A转换器。其中双极型开关D/A转换器又分为电流开关型和ECL电流开关型两种,在速度要求不高的情况下,可选用CMOS开关型D/A转换器。如果要求较高的转换速度则应选用双极型电流开关D/A转换器或转换速度更高的ECL电流开关型D/A转换器。

在单片集成D/A转换器中,使用最多的是倒T形电阻网络D/A转换器c下面以4位D/A转换器为例说明其工作原理。

Virtex系列为高密度、高性能产品。其中Ⅴirtex-E(1.8Ⅴ核心工作电压)和Virtex-Ⅱ(1.5V核心工作电压)也已逐渐成为主流产品。Ⅴirtex-Ⅱ内部时钟工作频率可达420 MHz,且内部已集成了18×18乘法器。表7.4,6所示为几种典型的FPGA产品规模。由表中看出,XC2Ⅴ8000最大可用引脚数已达1108个。

Xilinx公司几种典型的FPG实现逻辑功能元的组织方式公司外,Altera也是最大的可编程逻辑器件供应商之一,基本原理类似于Xilinx公司的FPGA。它们的主要区别和内部连接布线方式不同。Altera的FPGA中逻辑块所其FPGA是逻辑单包含的逻辑单元较多,一般为8个以上。内连方式采用纵横交错的快速互联通道(Fast~Track),没有用开关矩阵,信号的传输延时一致性较好。Altera FPGA的产品主要有FLEⅩ、APEX、straux、cyclone、MAXII等。其中FLEX和APEX属于20世纪90年代末的产品,目前逐渐被stratix和Cyclone取代。

spanan-Ⅱ系列的FPGA中,1个CLB有几个微中有几个LUT?

几个触发器?1个CLB能实现多少变量的任意逻辑函数?

可编程开关点(图7.3.4)和可编程开关矩阵中的连接点有何区别?

为什么在FPGA构成的数字系统中要配各一个PROM或EPROM?

FPGA与CPLD有哪些主要区别?它们各有什么特点?

设计一个定时器。要求:定时时间为24s,按递减方式计时,每隔1s,定时器减1。

设置两个外部控制开关(控制功能如表7.5.1所示),控制定时器的直接复位、启动计时、暂停/连续计时。

当定时器递减计时到零(即定时时间到)时,定时器保持零不变,同时发出报警信号。

输入时钟脉冲的频率为1 Hz,输出为8421表7.5.1 定时器功能表BCD码。

解:(1)逻辑设计,用计数器对1 Hz的时钟信号进行计数,其计数值即为定时时间。根据设计要求可知,电路需要输出2组8421BCD码,计数器初值为24,按递减方式计数,减到0时,输出报警信号,并能控制计数器暂停/连续计数,所以需要

设计一个可预置初值的带使能控制端的递减计数器。

实现上述功能的Verilog HDL程序如下。HDL描述分为3部分:第一部分定义了电路的输入、输出信号。其输入信号为复位nRsT(低电平有效)、暂停/连续nPAusE和时钟CP。输出信号为TimerH(定时器的十位)、TimerL(定时器的个位)和报警Alarm。第二部分用一个连续赋值语句assign说明当计数器递减到0时,输出报警信号(Alarm=1)。第三部分用一个过程块always说明计数器的计数、处理操作,计数器的个位和十位均按8421BCD码方式递减计数。

公网安备44030402000607

公网安备44030402000607