M29W128FL输出转折点的电压值

发布时间:2019/10/12 17:57:25 访问次数:978

M29W128FL当输入增加到vI≥vtD时,T1管导通,但最初吒仍为2.1V,使T1管工作在饱和区,并产生漏极电流J1,致使流入T4管电流氵L减少。但T4仍然导通,则输出电压的值仍接近于0.7V。当v1增加至-0.26Ⅴ时,i1+i3=i2,使jL=0,T4截止。

继续增加vI,吒下降使%>v′。+|%D|时,T1进入可变电阻区,吒输出电压约为0,17V。此时,T2和T3仍工作在饱和区,D1、D2保持导通,o。=-2%+吒=-1・23Ⅴ。当输人达到高电平电压一0.16Ⅴ以后,输出电压下降到-1.27V的低电平。

上述输入、输出转折点的电压值,可以根据MESFET工作在不同区域时的JD与vGs及″Ds关系进行计算,详细内容可以参阅参考文献[1]。

耗尽型MESFET逻辑电路的噪声容限比直接耦合逻辑电路的噪声容限高,但电路要求两个供电电源。

砷化镓器件最突出的优点是工作速度比硅器仵快得多,门传输延迟时间为10~100 ps。其缺点是功耗较大,逻辑摆幅小,因此噪声容限低,抗干扰能力较差。目前砷化镓技术主要用于小规模、中规模和大规模集成电路的生产。

为什么砷化镓器件比硅器件速度快?

现在应用较多的有哪几种类型的逻辑电路?

正负逻辑问题,正负逻辑的规定,在数字电路中,可以采用两种不同的逻辑体制表示电路输人和输出的高、低电平。在前面讨论时,将高电平用逻辑1表示,低电平用逻辑0表示,这种表示方法称为正逻辑体制。如果将高电平用逻辑0表示,低电平用逻辑1表示,则这种表示方法称为负逻辑体制。

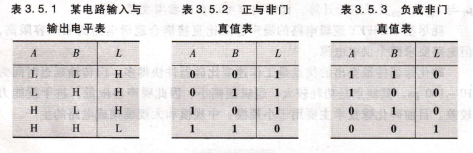

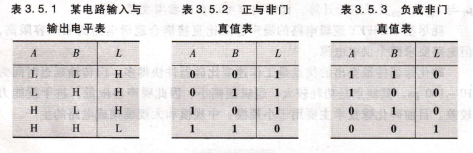

对于同一电路的输入与输出关系的描述,可以采用正逻辑,也可以采用负逻辑。正逻辑和负逻辑两种体制不牵涉逻辑电路本身的结构问题 ,但根据所选正负逻辑的不同,即使同一电路也具有不同的逻辑功能.例如某个逻辑门电路的输人和输出电平如表3.5,1所示,其中H和L分别表示高、低电平。如果采用正逻辑体制,令H=1,L=0,得到如表3.5,2所示的真值表,它表示与非逻辑关系L=A・B。如果采用负逻辑体制,令H=0,L=1,得到如表3,5.3所示的真值表,它表示或非逻辑关系L=A+B。因此,正逻辑的与非门等效于负逻辑的或非门。正逻辑和负逻辑只是看问题的角度或分析问题的方法不同而已,问题的实质是不变的,即电路输入与输出的电平关系始终是不变的。本书如无特殊说明,一律采用正逻辑,即规定高电平为逻辑1,低电平为逻辑0。

M29W128FL当输入增加到vI≥vtD时,T1管导通,但最初吒仍为2.1V,使T1管工作在饱和区,并产生漏极电流J1,致使流入T4管电流氵L减少。但T4仍然导通,则输出电压的值仍接近于0.7V。当v1增加至-0.26Ⅴ时,i1+i3=i2,使jL=0,T4截止。

继续增加vI,吒下降使%>v′。+|%D|时,T1进入可变电阻区,吒输出电压约为0,17V。此时,T2和T3仍工作在饱和区,D1、D2保持导通,o。=-2%+吒=-1・23Ⅴ。当输人达到高电平电压一0.16Ⅴ以后,输出电压下降到-1.27V的低电平。

上述输入、输出转折点的电压值,可以根据MESFET工作在不同区域时的JD与vGs及″Ds关系进行计算,详细内容可以参阅参考文献[1]。

耗尽型MESFET逻辑电路的噪声容限比直接耦合逻辑电路的噪声容限高,但电路要求两个供电电源。

砷化镓器件最突出的优点是工作速度比硅器仵快得多,门传输延迟时间为10~100 ps。其缺点是功耗较大,逻辑摆幅小,因此噪声容限低,抗干扰能力较差。目前砷化镓技术主要用于小规模、中规模和大规模集成电路的生产。

为什么砷化镓器件比硅器件速度快?

现在应用较多的有哪几种类型的逻辑电路?

正负逻辑问题,正负逻辑的规定,在数字电路中,可以采用两种不同的逻辑体制表示电路输人和输出的高、低电平。在前面讨论时,将高电平用逻辑1表示,低电平用逻辑0表示,这种表示方法称为正逻辑体制。如果将高电平用逻辑0表示,低电平用逻辑1表示,则这种表示方法称为负逻辑体制。

对于同一电路的输入与输出关系的描述,可以采用正逻辑,也可以采用负逻辑。正逻辑和负逻辑两种体制不牵涉逻辑电路本身的结构问题 ,但根据所选正负逻辑的不同,即使同一电路也具有不同的逻辑功能.例如某个逻辑门电路的输人和输出电平如表3.5,1所示,其中H和L分别表示高、低电平。如果采用正逻辑体制,令H=1,L=0,得到如表3.5,2所示的真值表,它表示与非逻辑关系L=A・B。如果采用负逻辑体制,令H=0,L=1,得到如表3,5.3所示的真值表,它表示或非逻辑关系L=A+B。因此,正逻辑的与非门等效于负逻辑的或非门。正逻辑和负逻辑只是看问题的角度或分析问题的方法不同而已,问题的实质是不变的,即电路输入与输出的电平关系始终是不变的。本书如无特殊说明,一律采用正逻辑,即规定高电平为逻辑1,低电平为逻辑0。

公网安备44030402000607

公网安备44030402000607