被测CPU特点

发布时间:2019/6/21 21:36:39 访问次数:671

被测器件介绍

被测CPU特点:

sOC架构,器件引脚数达12O0多个;

片上集成12个对称核心; A1101EUA-T

集成多个DDR3接口、PCI-E2.0和GMAC被测CPU结构框图如图⒋35所示。

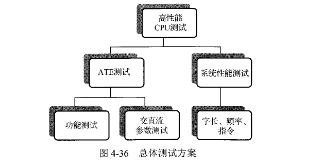

总体测试方案

本次测试采用的总体方案如图⒋36所示。

ATE测试主要包括如下项目。

连接性测试:测试通道与引脚接触性、电地短路测试;

功能测试:单核/多核功能、高速接口功能等测试;

直流参数如高低电平、漏电流等测试,交流参数(如输出延迟、建立、保持时间等测试);

功耗测试:静态功耗、各种功耗管理功能等测试;

电源拉偏测试:核心和V0电源的拉偏测试。

系统性能测试在特定的工程测试板上进行,工程测试板不同于ATE坝试板,其包含了更多、更为复杂的外围电路及模块。系统性能测试如要包括如下项目。字长、频率、功耗测试;

CPU核的数量测试;

CPU运算性能测试;

CPU系统综合性能测试;

缓存性能测试;

多核协同性测试;

电源拉偏测试:核心和y0电源的拉偏测试。

被测器件介绍

被测CPU特点:

sOC架构,器件引脚数达12O0多个;

片上集成12个对称核心; A1101EUA-T

集成多个DDR3接口、PCI-E2.0和GMAC被测CPU结构框图如图⒋35所示。

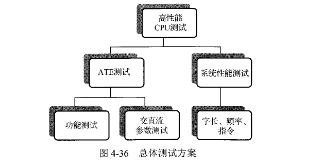

总体测试方案

本次测试采用的总体方案如图⒋36所示。

ATE测试主要包括如下项目。

连接性测试:测试通道与引脚接触性、电地短路测试;

功能测试:单核/多核功能、高速接口功能等测试;

直流参数如高低电平、漏电流等测试,交流参数(如输出延迟、建立、保持时间等测试);

功耗测试:静态功耗、各种功耗管理功能等测试;

电源拉偏测试:核心和V0电源的拉偏测试。

系统性能测试在特定的工程测试板上进行,工程测试板不同于ATE坝试板,其包含了更多、更为复杂的外围电路及模块。系统性能测试如要包括如下项目。字长、频率、功耗测试;

CPU核的数量测试;

CPU运算性能测试;

CPU系统综合性能测试;

缓存性能测试;

多核协同性测试;

电源拉偏测试:核心和y0电源的拉偏测试。

公网安备44030402000607

公网安备44030402000607