分离的I/0地

发布时间:2014/4/19 17:05:48 访问次数:561

如果I/O连接器和(或)电缆滤波电容被安装在PCB上,则需要设置到PCB上外壳地的接口。SN74HC595DR除非在设计初期考虑,等需要的时候再考虑这样的地就不可用了。

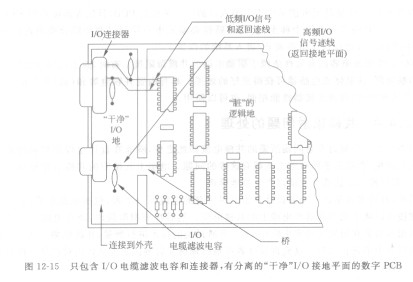

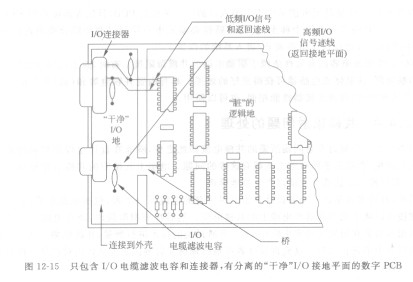

把历有的I/O连接器都放在板的一个区域内,而且在这个区域内设置分离的I/O接地平面,以低阻抗连接到外壳并且只在一点连接到数字逻辑地,就可以实现这种接口。用这个方法,没有嘈杂的数字逻辑地电流流过“干净”的I/O地去污染它。

图12-15给出了这个想法一个可能的实现方法。为了避免污染I/O接地平面,与其连接的唯一组件应是I/O电缆滤波电容和I/O连接头的背面。这个地必须与外壳有低阻抗连接。

I/O接地平面应与外壳有多重连接以使它的电感最小化,并提供一个低阻抗连接。如果I/O地和外壳地之间的连接没有建立,或如果没有足够低的阻抗(在有关的频率处),I/O接地平面将不再有效,而事实上,用这种设计方法,电缆的发射可能实际增加了。然而当方法正确时,这个方法工作良好,而且已经被成功地应用在许多商业产品中。

如果设计合理,跨I/O接地平面缝隙的迹线将不再是个问题。低频I/O信号(小于5~10MHz)应如图12-15所示用两个迹线(一个信号迹线和一个伴行返回迹线)在驱动IC和连接器之间连接。因此,信号返回电流是在伴行迹线中而不在接地面中。伴行返回迹线只与I/O连接器插脚连接而不与I/O接地面连接。

高频I/O信弓(高于5~10MHz)可以邻近接地面布置为单一信号迹线,只要布置迹线跨一个桥,如图12-15中所示。这种方法在迹线下为返回电流提供了一个连续的路径,这与图17-l(b)中所示的有关混合信号PCB布设的方法相似。桥应该足够宽以容纳所需的迹线数加上每一边接地面上迹线高度的20倍(对于0.005in高的迹线是0.lin)。见表17―1,这将使桥足够宽以适合97%的返回电流。

如果I/O连接器和(或)电缆滤波电容被安装在PCB上,则需要设置到PCB上外壳地的接口。SN74HC595DR除非在设计初期考虑,等需要的时候再考虑这样的地就不可用了。

把历有的I/O连接器都放在板的一个区域内,而且在这个区域内设置分离的I/O接地平面,以低阻抗连接到外壳并且只在一点连接到数字逻辑地,就可以实现这种接口。用这个方法,没有嘈杂的数字逻辑地电流流过“干净”的I/O地去污染它。

图12-15给出了这个想法一个可能的实现方法。为了避免污染I/O接地平面,与其连接的唯一组件应是I/O电缆滤波电容和I/O连接头的背面。这个地必须与外壳有低阻抗连接。

I/O接地平面应与外壳有多重连接以使它的电感最小化,并提供一个低阻抗连接。如果I/O地和外壳地之间的连接没有建立,或如果没有足够低的阻抗(在有关的频率处),I/O接地平面将不再有效,而事实上,用这种设计方法,电缆的发射可能实际增加了。然而当方法正确时,这个方法工作良好,而且已经被成功地应用在许多商业产品中。

如果设计合理,跨I/O接地平面缝隙的迹线将不再是个问题。低频I/O信号(小于5~10MHz)应如图12-15所示用两个迹线(一个信号迹线和一个伴行返回迹线)在驱动IC和连接器之间连接。因此,信号返回电流是在伴行迹线中而不在接地面中。伴行返回迹线只与I/O连接器插脚连接而不与I/O接地面连接。

高频I/O信弓(高于5~10MHz)可以邻近接地面布置为单一信号迹线,只要布置迹线跨一个桥,如图12-15中所示。这种方法在迹线下为返回电流提供了一个连续的路径,这与图17-l(b)中所示的有关混合信号PCB布设的方法相似。桥应该足够宽以容纳所需的迹线数加上每一边接地面上迹线高度的20倍(对于0.005in高的迹线是0.lin)。见表17―1,这将使桥足够宽以适合97%的返回电流。

上一篇:屏蔽层通过一个小辫终止于外壳

上一篇: I/O的地应该被看成是外壳的延伸

热门点击

热门点击

- RC移相式正弦波振荡器电路故障分析

- 多谐振荡器电路又称为无稳态电路

- 元器件焊接操作方法

- 电流串联负反馈电路

- 功率晶体管的开关作用

- 电子系统中静电放电感应效应可分为以下三类

- 在近场金属屏蔽层磁衰减实验数据

- 正、负极性半波整流电路

- 万用表检修特殊扬声器电路故障

- 同步分离电路

推荐技术资料

推荐技术资料

- FU-19推挽功放制作

- FU-19是国产大功率发射双四极功率电二管,EPL20... [详细]

公网安备44030402000607

公网安备44030402000607