栅极接地电路的设计

发布时间:2012/8/19 16:00:44 访问次数:1027

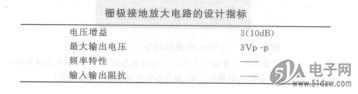

图6.1电路的设计指VIPER22A标如下表所示。为了便于对电路本身的性能进行比较,这些指标与第3章源极接地放大电路的设计指标相同。

电源电压与FET的选择

与源极接地电路相同,电源电压取值应该比最大输出电压十源极电阻(本电路中是Rs+R。)上的电压降(最低1~2V)之和大。在这个电路中还要加上OP放大器的电源电压,所以取VDD =15V。

为了便于分析源极接地与栅极接地电路结构的性能差别,FET也选用与源极接地电路相同的N沟JFET 2SK184GR。

栅极接地电路中选择FET的基准也与源极接地电路相同:栅极一漏极间电压的最大额定值VGDS高于电源电压(在本电路中VGDs>VDD一15V),漏极饱和电流IDSS要比电路中设定的漏极电流大(关于漏极电流,在选定FET后可以设定低于IDSS)。当然,使用MOSFET时就没有必要考虑IDSS了。

图6.1电路的设计指VIPER22A标如下表所示。为了便于对电路本身的性能进行比较,这些指标与第3章源极接地放大电路的设计指标相同。

电源电压与FET的选择

与源极接地电路相同,电源电压取值应该比最大输出电压十源极电阻(本电路中是Rs+R。)上的电压降(最低1~2V)之和大。在这个电路中还要加上OP放大器的电源电压,所以取VDD =15V。

为了便于分析源极接地与栅极接地电路结构的性能差别,FET也选用与源极接地电路相同的N沟JFET 2SK184GR。

栅极接地电路中选择FET的基准也与源极接地电路相同:栅极一漏极间电压的最大额定值VGDS高于电源电压(在本电路中VGDs>VDD一15V),漏极饱和电流IDSS要比电路中设定的漏极电流大(关于漏极电流,在选定FET后可以设定低于IDSS)。当然,使用MOSFET时就没有必要考虑IDSS了。

上一篇:漂极波形与漏极波形同相

上一篇:确定RS、R3、RD的方法

公网安备44030402000607

公网安备44030402000607