低残留波纹电源电路

发布时间:2012/5/16 20:08:11 访问次数:1631

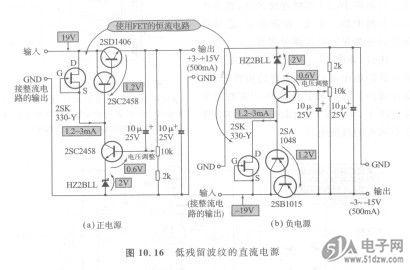

图10.16是提高误差放大SW-277TR器的增益,使得残留波纹进一步减少的电源电路。当增大误差放大器的增益时,增益变大的份量全部变成负反馈,能够将输出电压的波纹成分减少同样份量的值。

在图10.5所示的电路中,误差放大器使用的共发射极放大电路的负载上使用电阻(图10.5的R1),但在图10. 16的电路中,共发射极电路的负载是使用JFET(结型FET)的稳流电路。由于稳流电路的内部电阻几乎是无限大,故该共发射极电路的增益非常大。

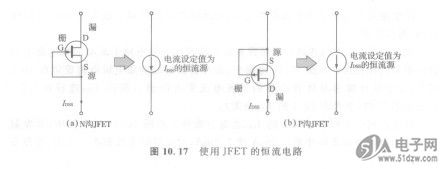

如图10.17所示,当JFET的栅极与源极相连接时,可以作为稳流源来使用。此时的稳流源的设定电流就是JFET的漏饱和电流IDSS本身。

所谓JFET的IDSS,就是在漏一源之间流动的最大电流(是不损坏器件为限界,在JFET中不能流过IDSS以上的电流)。

通常,JFET是根据IDSS的大小来进行分档的(即使是同一品种,JFET的IDSS也有很大的分散性,所以可进行分档),选择与稳流源设定电流值相等的IDSS的JFET即可。

除了选择JFET之外,图10.16电路的设计方法均与图10.5完全相同(除了JFET之外,图10.16(a)电路其余的常数均与图10.5相同)。

图10.16是提高误差放大SW-277TR器的增益,使得残留波纹进一步减少的电源电路。当增大误差放大器的增益时,增益变大的份量全部变成负反馈,能够将输出电压的波纹成分减少同样份量的值。

在图10.5所示的电路中,误差放大器使用的共发射极放大电路的负载上使用电阻(图10.5的R1),但在图10. 16的电路中,共发射极电路的负载是使用JFET(结型FET)的稳流电路。由于稳流电路的内部电阻几乎是无限大,故该共发射极电路的增益非常大。

如图10.17所示,当JFET的栅极与源极相连接时,可以作为稳流源来使用。此时的稳流源的设定电流就是JFET的漏饱和电流IDSS本身。

所谓JFET的IDSS,就是在漏一源之间流动的最大电流(是不损坏器件为限界,在JFET中不能流过IDSS以上的电流)。

通常,JFET是根据IDSS的大小来进行分档的(即使是同一品种,JFET的IDSS也有很大的分散性,所以可进行分档),选择与稳流源设定电流值相等的IDSS的JFET即可。

除了选择JFET之外,图10.16电路的设计方法均与图10.5完全相同(除了JFET之外,图10.16(a)电路其余的常数均与图10.5相同)。

热门点击

热门点击

公网安备44030402000607

公网安备44030402000607