异步计数器

发布时间:2012/2/16 20:13:42 访问次数:1764

与同步计数器相比,异步计数器具有结构简单的优点。但异步计数器也存在两个明显的缺点:一个是工作频率比较低,因为异步计数器的各级触发器是以串行进位方式连接的;第二个是触发器输出端状态的建立要比CP下降沿滞后一个传输延迟时间,在电路状态译码时存在竞争冒险现象。RHF350K1

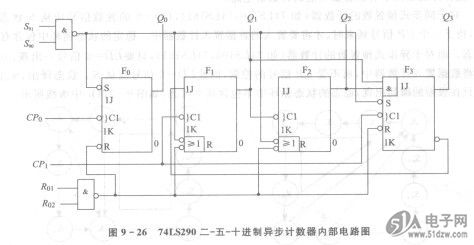

这里仅以74LS290为例,74LS290是二一五一十进制异步计数器,它的逻辑电路如囹9- 26所示。从图中可以看出时钟输入端是的时钟是Ql,而F,和F3的时钟是另外一个输入端CP1引入。

电路若以CP。为计数脉冲输入端、Q。为输出端,即得到二进制计数器(或二分频器);若以CP.作为计数脉冲输入端、Q。为输出端,则得到五进制计数器(或五分频器);若将CPi与Qo相连,同时以CP。,为计数脉冲输入端、Q3为输出端,则得到十进制计数器(或十分频器)。

与同步计数器相比,异步计数器具有结构简单的优点。但异步计数器也存在两个明显的缺点:一个是工作频率比较低,因为异步计数器的各级触发器是以串行进位方式连接的;第二个是触发器输出端状态的建立要比CP下降沿滞后一个传输延迟时间,在电路状态译码时存在竞争冒险现象。RHF350K1

这里仅以74LS290为例,74LS290是二一五一十进制异步计数器,它的逻辑电路如囹9- 26所示。从图中可以看出时钟输入端是的时钟是Ql,而F,和F3的时钟是另外一个输入端CP1引入。

电路若以CP。为计数脉冲输入端、Q。为输出端,即得到二进制计数器(或二分频器);若以CP.作为计数脉冲输入端、Q。为输出端,则得到五进制计数器(或五分频器);若将CPi与Qo相连,同时以CP。,为计数脉冲输入端、Q3为输出端,则得到十进制计数器(或十分频器)。

上一篇:计时器时序

上一篇:集成计数器的应用方法和举例

公网安备44030402000607

公网安备44030402000607