同步时序逻辑电路设计

发布时间:2011/9/6 17:05:52 访问次数:2897

在设计时序逻辑电路时,要求设计者根据给出的具体逻辑问题,求出实现这一逻辑功能的逻辑电路。所得到的设计结果应力求简单。在这一小节里首先讨论简单时序电路的设计。这里所说的简单时序电路,是指用一组状态方程、驱动方程和输出方程就能完全描述其逻辑功能的时序电路。 BFU630F

当选用小规模集成电路做设计时,电路最简的标准是所用的触发器和门电路的数目最少,而且触发器和门电路的输入端数目也最少。而当使用中、大规模集成电路时,电路最简的标准则是使用的集成电路数目最少,种类最少,而且互相间的连线也最少。

设计同步时序逻辑电路时,一般按如下步骤进行。

(1)逻辑抽象,得出电路的状态转换图或状态转换表

就是将要求实现的时序逻辑功能表示为时序逻辑函数,可以用状态转换表的形式,也可以用状态转换图或状态流程图的形式。这就需要:

①分析给定的逻辑问题,确定输入变量、输出变量以及电路的状态数。通常都是取原因(或条件)作为输入逻辑变量,取结果作输出逻辑变量。

②定义输入、输出逻辑状态和每个电路状态的含意,并将电路扶态顺序编号。

③按照题意列出电路的状态转换表或画出电路的状态转换图。

这样,就把给定的逻辑问题抽象为一个时序逻辑函数了。

(2)状态化简

若两个电路状态在相同的输入下有相同的输出,并且转换到同样一个次态去,则称这两个状态为等价状态。显然,等价状态是重复的,可以合并为一个。电路的状态数越少,设计出来的电路就超简单。

状态化简的目的就在于将等价状态合并,以求得最简的状态转换图。

(3)状态分配

状态分配又称状态编码。

时序逻辑电路的状态是用触发器状态的不同组合来表示的。首先,需要确定触发器的数目n。因为行个触发器共有2n种状态组合,所以为获得时序电路所需的M个状态,必须取

2n-1<M≤2n

其次,要给每个电路状态规定对应的触发器状态组合。每组触发器的状态组合都是一组二值代码,因而又将这项工作称为状态编码。在M<2n的情况下,从2n个状态中取M个状态的组合可以有多种不同的方案,而每个方案中M个状态的排列顺序又有许多种。如果编码方案选择得当,设计结果可以很简单。反之,编码方案选得不好,设计出来的电路就会复杂得多,这里面有一定的技巧。

此外,为便于记忆和识别,一般选用的状态编码和它们的排列顺序都遵循一定的规律。

(4)求出电路的状态方程、驱动方程和输出方程

因为不同逻辑功能的触发器驱动方式不同,所以用不同类型触发器设计出的电路也不一样。为此,在设计具体的电路前必须选定触发器的类型。选择触发器类型时应考虑到器件的供应情况,井应力求减少系统中使用的触发器种类。

根据状态转换图(或状态转换表)和选定的状态编码、触发器的类型,就可以写出电路的状态方程、驱动方程和输出方程了。

(5)根据得到的方程式画出逻辑图

(6)检查设计的电路能否自启动

如果电路不能自启动,则需采取措施加以解决。一种解决办法是在电路开始工作时通过预置数将电路的状态置成有效状态循环中的某一种。另一种解决方法是通过修改逻辑设计加以解决。 BSM100GP60

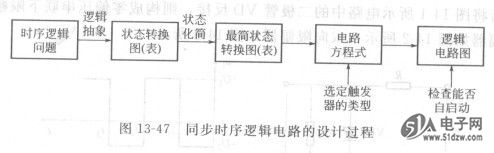

至此,逻辑设计工作已经完成。图13-47用方框图表示了上述设计工作的大致过程。不难看出,这一过程和分析时序电路的过程正好是相反的。

在设计时序逻辑电路时,要求设计者根据给出的具体逻辑问题,求出实现这一逻辑功能的逻辑电路。所得到的设计结果应力求简单。在这一小节里首先讨论简单时序电路的设计。这里所说的简单时序电路,是指用一组状态方程、驱动方程和输出方程就能完全描述其逻辑功能的时序电路。 BFU630F

当选用小规模集成电路做设计时,电路最简的标准是所用的触发器和门电路的数目最少,而且触发器和门电路的输入端数目也最少。而当使用中、大规模集成电路时,电路最简的标准则是使用的集成电路数目最少,种类最少,而且互相间的连线也最少。

设计同步时序逻辑电路时,一般按如下步骤进行。

(1)逻辑抽象,得出电路的状态转换图或状态转换表

就是将要求实现的时序逻辑功能表示为时序逻辑函数,可以用状态转换表的形式,也可以用状态转换图或状态流程图的形式。这就需要:

①分析给定的逻辑问题,确定输入变量、输出变量以及电路的状态数。通常都是取原因(或条件)作为输入逻辑变量,取结果作输出逻辑变量。

②定义输入、输出逻辑状态和每个电路状态的含意,并将电路扶态顺序编号。

③按照题意列出电路的状态转换表或画出电路的状态转换图。

这样,就把给定的逻辑问题抽象为一个时序逻辑函数了。

(2)状态化简

若两个电路状态在相同的输入下有相同的输出,并且转换到同样一个次态去,则称这两个状态为等价状态。显然,等价状态是重复的,可以合并为一个。电路的状态数越少,设计出来的电路就超简单。

状态化简的目的就在于将等价状态合并,以求得最简的状态转换图。

(3)状态分配

状态分配又称状态编码。

时序逻辑电路的状态是用触发器状态的不同组合来表示的。首先,需要确定触发器的数目n。因为行个触发器共有2n种状态组合,所以为获得时序电路所需的M个状态,必须取

2n-1<M≤2n

其次,要给每个电路状态规定对应的触发器状态组合。每组触发器的状态组合都是一组二值代码,因而又将这项工作称为状态编码。在M<2n的情况下,从2n个状态中取M个状态的组合可以有多种不同的方案,而每个方案中M个状态的排列顺序又有许多种。如果编码方案选择得当,设计结果可以很简单。反之,编码方案选得不好,设计出来的电路就会复杂得多,这里面有一定的技巧。

此外,为便于记忆和识别,一般选用的状态编码和它们的排列顺序都遵循一定的规律。

(4)求出电路的状态方程、驱动方程和输出方程

因为不同逻辑功能的触发器驱动方式不同,所以用不同类型触发器设计出的电路也不一样。为此,在设计具体的电路前必须选定触发器的类型。选择触发器类型时应考虑到器件的供应情况,井应力求减少系统中使用的触发器种类。

根据状态转换图(或状态转换表)和选定的状态编码、触发器的类型,就可以写出电路的状态方程、驱动方程和输出方程了。

(5)根据得到的方程式画出逻辑图

(6)检查设计的电路能否自启动

如果电路不能自启动,则需采取措施加以解决。一种解决办法是在电路开始工作时通过预置数将电路的状态置成有效状态循环中的某一种。另一种解决方法是通过修改逻辑设计加以解决。 BSM100GP60

至此,逻辑设计工作已经完成。图13-47用方框图表示了上述设计工作的大致过程。不难看出,这一过程和分析时序电路的过程正好是相反的。

上一篇:二极管钳位器

公网安备44030402000607

公网安备44030402000607