��ѹ���ƾ���ܵ�ͨ���Էŵ�ЧӦ

����ʱ��:2020/11/15 22:18:58 ���ʴ���:1155

ÿ����Ԫ�洢һ�����أ�һ����4���ش洢����ÿһ�еĵ�ѹ���ƾ���ܵ�ͨ�ϣ�������صĵ��ݳ���ŵ硣��ÿ������ġ����ߡ����֮����ѡ����ѡ���Ӧ�ĵ��ݣ����������Ķ�/д�����������Էŵ�ЧӦ����Щ��Ԫ����������ˢ�£�������������д�صIJ�����

SDRAMλ��Ԫ��SDRAMоƬ����֯�ṹ,SDRAM�ܹ���������洢��Ԫ����Щ�洢��Ԫ����к��еĶ�ά���С�Ҫѡ��ijһ�����أ�������ȷ����Ӧ���У�Ȼ��ȷ����Ӧ���С�����Ӧ���п���ʱ�����Է��ʶ���У��Ӷ����������/д���ٶȲ������ӳ١�

Ϊ���������������洢��ʹ�ö�����У���������Ҫ����һ�ζ�/д����ʱ���洢��ֻ��ҪѰַһ�η���ÿ�������е�1�����ء�

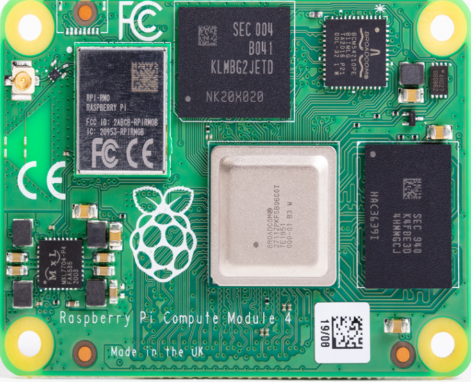

STM32WB55xx��STM32WB35xx�Ƕ�Э�����ߺͳ�����32λMCU,Ƕ���˹���ǿ��ͳ���������������SIGָ��v5.0�Լ�EEE 802.15.4-2011���ݵ����ߵ�.������������Arm® Cortex® -M0+,����ʵ������ʵʱ�Ͳ����.�������ڹ���Ƶ�ʸߴ�65MHz�ĸ�����Arm® Cortex®-M4 32λRISC��,�����и��㵥Ԫ(FPU)������,֧�����е�Arm®���������ݴ���ָ�����������,����ʵ������DSPָ��ʹ洢��������Ԫ(MPU),�Ӷ���ǿ��Ӧ�ð�ȫ��.

ʵʱ�洢ǰ����������غɻ���֧��GHz I/O���ʵ�FPGA���洢��������ADC��DAC�����磬һ��12λ1.5Gsps�����ʵ�ADCÿ�����18Gb��ԭʼ���ݡ�һ���ӵ�ѹ��SAR��Ϣ��Ҫ��Լ70Gb�Ĵ洢������������е�����洢�����������I/O����������ʱ�䡢���ġ������ߴ�ʹ洢��������˺ܴ����ս��

Ϊ�����Ӵ洢��������������SDRAM���ڲ�������������bank����Щbank���ཻ֯����һ����������ܣ������Զ���Ѱַ��

����Ҫִ�ж���д����ʱ�����ȴ洢������������ACTIVE��������Ӧ���к�bank������ִ����Ϻ�PRECHARGE����ر�һ������bank�е�һ����Ӧ���С�����֮ǰ���б��رգ����������µ��С�

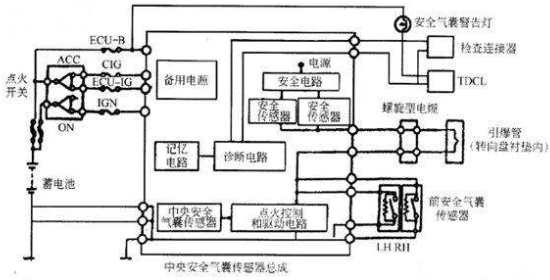

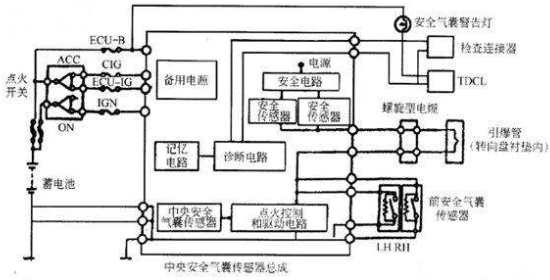

SDRAM�IJ���ͨ�����µĿ����ź�ʵ�֣�Ƭѡ(CS)����������(DQM)��дʹ��(WE)���е�ַѡͨ(RAS)���е�ַѡͨ(CAS)��

ÿ����Ԫ�洢һ�����أ�һ����4���ش洢����ÿһ�еĵ�ѹ���ƾ���ܵ�ͨ�ϣ�������صĵ��ݳ���ŵ硣��ÿ������ġ����ߡ����֮����ѡ����ѡ���Ӧ�ĵ��ݣ����������Ķ�/д�����������Էŵ�ЧӦ����Щ��Ԫ����������ˢ�£�������������д�صIJ�����

SDRAMλ��Ԫ��SDRAMоƬ����֯�ṹ,SDRAM�ܹ���������洢��Ԫ����Щ�洢��Ԫ����к��еĶ�ά���С�Ҫѡ��ijһ�����أ�������ȷ����Ӧ���У�Ȼ��ȷ����Ӧ���С�����Ӧ���п���ʱ�����Է��ʶ���У��Ӷ����������/д���ٶȲ������ӳ١�

Ϊ���������������洢��ʹ�ö�����У���������Ҫ����һ�ζ�/д����ʱ���洢��ֻ��ҪѰַһ�η���ÿ�������е�1�����ء�

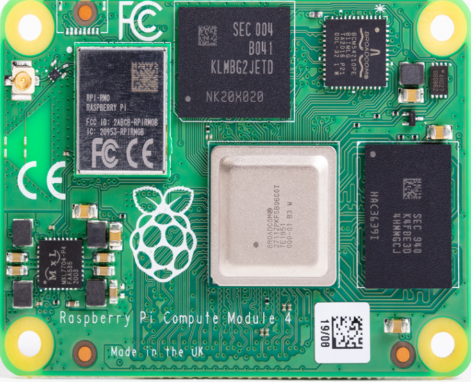

STM32WB55xx��STM32WB35xx�Ƕ�Э�����ߺͳ�����32λMCU,Ƕ���˹���ǿ��ͳ���������������SIGָ��v5.0�Լ�EEE 802.15.4-2011���ݵ����ߵ�.������������Arm® Cortex® -M0+,����ʵ������ʵʱ�Ͳ����.�������ڹ���Ƶ�ʸߴ�65MHz�ĸ�����Arm® Cortex®-M4 32λRISC��,�����и��㵥Ԫ(FPU)������,֧�����е�Arm®���������ݴ���ָ�����������,����ʵ������DSPָ��ʹ洢��������Ԫ(MPU),�Ӷ���ǿ��Ӧ�ð�ȫ��.

ʵʱ�洢ǰ����������غɻ���֧��GHz I/O���ʵ�FPGA���洢��������ADC��DAC�����磬һ��12λ1.5Gsps�����ʵ�ADCÿ�����18Gb��ԭʼ���ݡ�һ���ӵ�ѹ��SAR��Ϣ��Ҫ��Լ70Gb�Ĵ洢������������е�����洢�����������I/O����������ʱ�䡢���ġ������ߴ�ʹ洢��������˺ܴ����ս��

Ϊ�����Ӵ洢��������������SDRAM���ڲ�������������bank����Щbank���ཻ֯����һ����������ܣ������Զ���Ѱַ��

����Ҫִ�ж���д����ʱ�����ȴ洢������������ACTIVE��������Ӧ���к�bank������ִ����Ϻ�PRECHARGE����ر�һ������bank�е�һ����Ӧ���С�����֮ǰ���б��رգ����������µ��С�

SDRAM�IJ���ͨ�����µĿ����ź�ʵ�֣�Ƭѡ(CS)����������(DQM)��дʹ��(WE)���е�ַѡͨ(RAS)���е�ַѡͨ(CAS)��

�������

�������

- DSP48E2Ƭ�;���MAC���㼤���������

- ���籶���ܴ���������Ӧʱ����Ч��

- ����ƽ��ѹ�ӽ��ڵ�Դ��ѹ

- SRAM�ṹPIM����˫�˼ܹ����ŵ�

- BNCתSMA������������˫·������

- ����XGS����������FPGA���������Ľӿ�

- �������ͺ����ȳ����������ⷽ��

- ���ص�Դ�еķ����任��С���ʵ���

- ��Ƶ�ĸ߾��ܾ���;����˲���

- ��Դ�������ʵ�ָ����Ⱥ߷ֱ���

�Ƽ���������

�Ƽ���������

- �й���ý��ѧ��ý����ݿ�

- ��ý����ݿ�����ʽ¡ͯ���С�������i���ҹ���ֵܾȲ���... [��ϸ]

��������44030402000607

��������44030402000607