瞬态电流转换器速度有效低通滤波器

发布时间:2020/11/14 12:13:56 访问次数:628

滚动平均过采样技术使用缓冲区来存储样本以执行平均过程。滚动平均算法选择缓冲区中存储的最新M个样本,然后将所得之和除以M。在数字设计中,缓冲区需要额外的空间来创建额外的存储区。在滚动平均过采样技术中,小型ADC的缓冲存储容量有限,采用先进先出(FIFO)算法。

当缓冲区已满且有新的样本可用时,缓冲区中最早的数据会被丢弃,使用前面的示例采样数据,前八个采样结果填充FIFO缓冲区(S1至S8)。当出现新的样本数据(S9)时,S1从缓冲区中移出,S9插入缓冲区中。此过程随着新样本存储在缓冲区中而重复执行。

滚动平均过采样技术将最新的M个样本相加,并将总和除以M来计算平均值。算法将FIFO缓冲区中的四个样本B1至B4(这是最新的四个样本)相加,然后除以4。相同的FIFO缓冲位置参与平均,但这些缓冲区中的内容会改变。在M = 8的情况下,FIFO缓冲区中的所有样本都包含在求和运算中,然后除以8。

两种平均技术在AD7380系列产品中均可使用。每种技术有其适合的一系列应用。不过,每种技术有其自己的特点,具体应用必须考虑这些特点。正常平均过采样技术有如下特点:

性能更优,因为此技术对额外数据进行采样以求平均。

ODR较慢,因为样本数或OSR增加,使得应用可以使用较低的SCLK频率,从而降低总成本。

信号带宽明显小于转换速率,带宽限制类似于一个有效低通滤波器。

SNR与输入频率的关系,过采样频率响应

滚动平均过采样技术有如下特点:

采样速率可以变化,由应用通过引脚进行控制。

最高4 MSPS的快速采样速率。

由于缓冲区限制,参与平均的样本数以8为限。

信号带宽更宽。

分辨率更高(N)

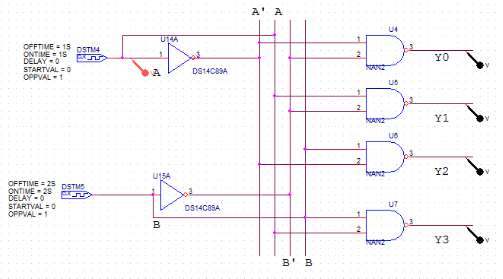

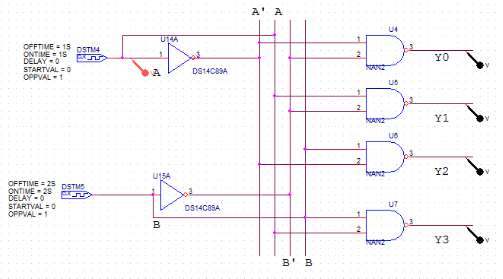

该瞬态电流是转换器速度超过200 MSPS时,输出驱动器采用其他技术的主要原因。

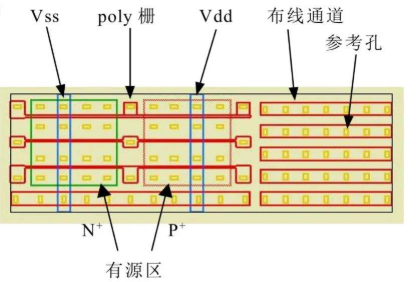

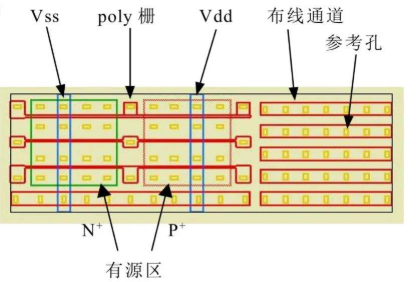

转换器的每一位也都需要CMOS驱动器。如果转换器有14位,就需要14个CMOS输出驱动器来传输这些位。一般会有一个以上的转换器置于单个封装中,常见为八个。采用CMOS技术时,意味着数据输出需要高达112个输出引脚。从封装角度来看,这不太可能实现,而且还会产生高功耗,并使电路板布局变得更加复杂。为了解决这些问题,我们引入了使用LVDS的接口。

LVDS数字输出驱动器与CMOS技术相比,LVDS具备一些明显优势。它可以在低电压信号(约350 mV)下工作,并且为差分而非单端。低压摆幅具有较快的切换时间,可以减少EMI问题。差分这一特性可以带来共模抑制的好处。

耦合到信号的噪声对两个信号路径均为共模,大部分都可被差分接收器消除。

(素材来源:21ic.如涉版权请联系删除。特别感谢)

滚动平均过采样技术使用缓冲区来存储样本以执行平均过程。滚动平均算法选择缓冲区中存储的最新M个样本,然后将所得之和除以M。在数字设计中,缓冲区需要额外的空间来创建额外的存储区。在滚动平均过采样技术中,小型ADC的缓冲存储容量有限,采用先进先出(FIFO)算法。

当缓冲区已满且有新的样本可用时,缓冲区中最早的数据会被丢弃,使用前面的示例采样数据,前八个采样结果填充FIFO缓冲区(S1至S8)。当出现新的样本数据(S9)时,S1从缓冲区中移出,S9插入缓冲区中。此过程随着新样本存储在缓冲区中而重复执行。

滚动平均过采样技术将最新的M个样本相加,并将总和除以M来计算平均值。算法将FIFO缓冲区中的四个样本B1至B4(这是最新的四个样本)相加,然后除以4。相同的FIFO缓冲位置参与平均,但这些缓冲区中的内容会改变。在M = 8的情况下,FIFO缓冲区中的所有样本都包含在求和运算中,然后除以8。

两种平均技术在AD7380系列产品中均可使用。每种技术有其适合的一系列应用。不过,每种技术有其自己的特点,具体应用必须考虑这些特点。正常平均过采样技术有如下特点:

性能更优,因为此技术对额外数据进行采样以求平均。

ODR较慢,因为样本数或OSR增加,使得应用可以使用较低的SCLK频率,从而降低总成本。

信号带宽明显小于转换速率,带宽限制类似于一个有效低通滤波器。

SNR与输入频率的关系,过采样频率响应

滚动平均过采样技术有如下特点:

采样速率可以变化,由应用通过引脚进行控制。

最高4 MSPS的快速采样速率。

由于缓冲区限制,参与平均的样本数以8为限。

信号带宽更宽。

分辨率更高(N)

该瞬态电流是转换器速度超过200 MSPS时,输出驱动器采用其他技术的主要原因。

转换器的每一位也都需要CMOS驱动器。如果转换器有14位,就需要14个CMOS输出驱动器来传输这些位。一般会有一个以上的转换器置于单个封装中,常见为八个。采用CMOS技术时,意味着数据输出需要高达112个输出引脚。从封装角度来看,这不太可能实现,而且还会产生高功耗,并使电路板布局变得更加复杂。为了解决这些问题,我们引入了使用LVDS的接口。

LVDS数字输出驱动器与CMOS技术相比,LVDS具备一些明显优势。它可以在低电压信号(约350 mV)下工作,并且为差分而非单端。低压摆幅具有较快的切换时间,可以减少EMI问题。差分这一特性可以带来共模抑制的好处。

耦合到信号的噪声对两个信号路径均为共模,大部分都可被差分接收器消除。

(素材来源:21ic.如涉版权请联系删除。特别感谢)

上一篇:更宽的带宽内对转换器噪声进行平均

公网安备44030402000607

公网安备44030402000607