光电编码器获得旋转机械的位置和速率

发布时间:2020/9/19 23:18:54 访问次数:1020

1 M点FFT分析中可以看出,在低于-111 dBc下具备不错的失真性能,在1 kHz输入频率下,10 kHz至200 kHz频段内出现最大杂散。噪声约为-146 dBFS。

对传统的AD1862进行测试,结果显示频率行为略微不同。在差分配置下,两个20位DAC的时钟速度约为500 kSPS,在1.130566 kHz下,本底噪声为-151 dBFS,正弦输出水平为12 V p-p时的THD为-104.5 dB。在AD4020 Nyquist带宽(806 kHz)下,SFDR接近106 dB,受三阶谐波限制。DAC重构滤波器基于两个AD743 <https://www.analog.com/en/products/ad743.html> 低噪声FET放大器,与AD1955评估板中的滤波器一样,属于三阶滤波器,但是-3 dB时的截止频率为35 kHz。

基于DDS的生成器需要采用不错的滤波器,支持在约250 kHz下实现大于100 dB衰减,以生成达到25 kHz CW信号频率范围的直流。这可以使用六阶切比雪夫滤波器实现,甚至使用用于显示出色带内平坦度的六阶巴特沃兹低通滤波器实现。滤波器阶将被最小化,以限制模拟级的数量和问题点,例如噪声和失真。

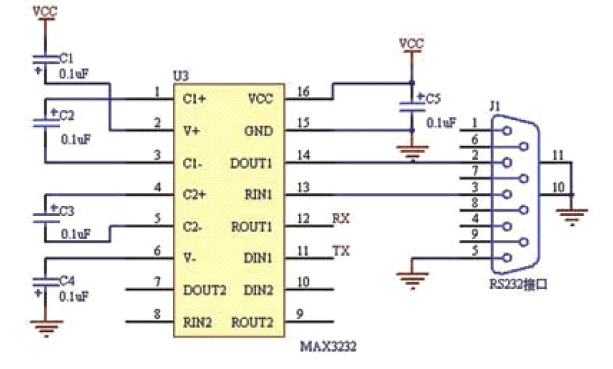

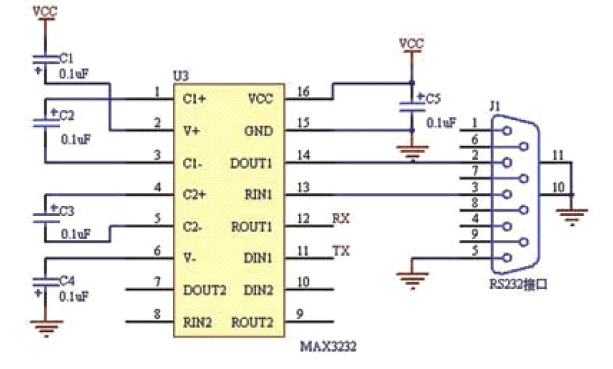

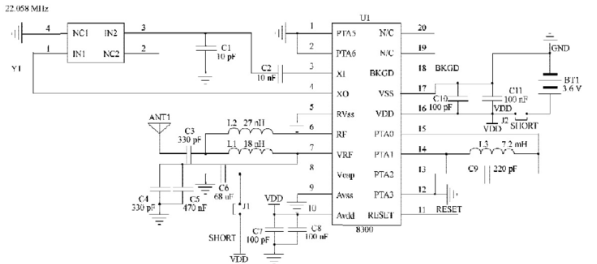

机械手视觉系统外围电路设计攻略,I\O 口:DSP 的数字I/O 口模块具有控制专用I/O 和复用引脚的功能,可以输出输入高低电平信号,根据其功能将其设计成开关量输出,输入,并用其控制继电器,作为控的开关。开关量输入只要用电阻分压即可,开关量输出使用光耦隔离,用的光耦PC817,比较适合DSP 使用。当DSP 输出高电平时继电器吸合,CNETA1 和CNETA2 两脚导通继电器电路.

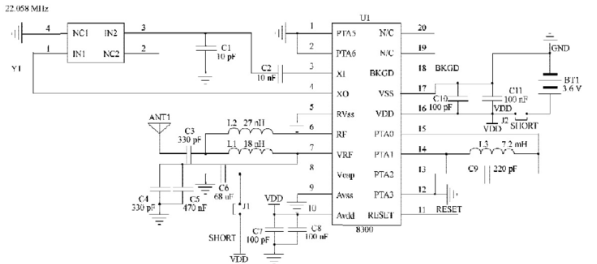

继电器QEP 电路:DSP 的每个时间管理器都有一个正交编码器脉冲(QEP)电路。当QEP电路被使能时可以对CAP1/QEP1 和CAP2/QEP2(对于EVA 模块)引脚上的正交编码输入脉冲进行解码和计数。正交编码脉冲电路可用于连接光电编码器以获得旋转机械的位置和速率。

伺服电机控制器需要使用QEP 电路,由于一个伺服电机控制器需要控制4 台伺服电机,所以码盘信号使用74153 芯片选择输入,同时码盘的每路信号都有正负两根线通过运放放大后再到74153 选择后输入DSP.

芯片都是2D平面堆叠的,随着芯片数量的增多,占用的面积越来越大,不利于提高集成度。关于3D芯片封装,就是将芯片从平面堆叠变成了垂直堆叠,类似搭积木那样一层层叠加,减少了芯片面积,提高了集成度。

衡量一个芯片封装技术先进与否的重要指标是:芯片面积与封装面积之比,这个比值越接近1越好,封装时主要考虑的因素:

芯片面积与封装面积之比,为提高封装效率,尽量接近1:1。

引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能。

基于散热的要求,封装越薄越好。

在三星推出X-Cube时,全球主要的三家半导体代工厂均已经拥有3D或2.5D的封装技术了。前有台积电的CoWoS,Intel的Foveros,现在三星也公布了自家的3D封装技术X-Cube。显而易见的是,未来我们买到的电子产品中,使用3D封装技术的芯片比例会越来越高。

(素材:chinaaet.如涉版权请联系删除)

(素材:chinaaet.如涉版权请联系删除)

1 M点FFT分析中可以看出,在低于-111 dBc下具备不错的失真性能,在1 kHz输入频率下,10 kHz至200 kHz频段内出现最大杂散。噪声约为-146 dBFS。

对传统的AD1862进行测试,结果显示频率行为略微不同。在差分配置下,两个20位DAC的时钟速度约为500 kSPS,在1.130566 kHz下,本底噪声为-151 dBFS,正弦输出水平为12 V p-p时的THD为-104.5 dB。在AD4020 Nyquist带宽(806 kHz)下,SFDR接近106 dB,受三阶谐波限制。DAC重构滤波器基于两个AD743 <https://www.analog.com/en/products/ad743.html> 低噪声FET放大器,与AD1955评估板中的滤波器一样,属于三阶滤波器,但是-3 dB时的截止频率为35 kHz。

基于DDS的生成器需要采用不错的滤波器,支持在约250 kHz下实现大于100 dB衰减,以生成达到25 kHz CW信号频率范围的直流。这可以使用六阶切比雪夫滤波器实现,甚至使用用于显示出色带内平坦度的六阶巴特沃兹低通滤波器实现。滤波器阶将被最小化,以限制模拟级的数量和问题点,例如噪声和失真。

机械手视觉系统外围电路设计攻略,I\O 口:DSP 的数字I/O 口模块具有控制专用I/O 和复用引脚的功能,可以输出输入高低电平信号,根据其功能将其设计成开关量输出,输入,并用其控制继电器,作为控的开关。开关量输入只要用电阻分压即可,开关量输出使用光耦隔离,用的光耦PC817,比较适合DSP 使用。当DSP 输出高电平时继电器吸合,CNETA1 和CNETA2 两脚导通继电器电路.

继电器QEP 电路:DSP 的每个时间管理器都有一个正交编码器脉冲(QEP)电路。当QEP电路被使能时可以对CAP1/QEP1 和CAP2/QEP2(对于EVA 模块)引脚上的正交编码输入脉冲进行解码和计数。正交编码脉冲电路可用于连接光电编码器以获得旋转机械的位置和速率。

伺服电机控制器需要使用QEP 电路,由于一个伺服电机控制器需要控制4 台伺服电机,所以码盘信号使用74153 芯片选择输入,同时码盘的每路信号都有正负两根线通过运放放大后再到74153 选择后输入DSP.

芯片都是2D平面堆叠的,随着芯片数量的增多,占用的面积越来越大,不利于提高集成度。关于3D芯片封装,就是将芯片从平面堆叠变成了垂直堆叠,类似搭积木那样一层层叠加,减少了芯片面积,提高了集成度。

衡量一个芯片封装技术先进与否的重要指标是:芯片面积与封装面积之比,这个比值越接近1越好,封装时主要考虑的因素:

芯片面积与封装面积之比,为提高封装效率,尽量接近1:1。

引脚要尽量短以减少延迟,引脚间的距离尽量远,以保证互不干扰,提高性能。

基于散热的要求,封装越薄越好。

在三星推出X-Cube时,全球主要的三家半导体代工厂均已经拥有3D或2.5D的封装技术了。前有台积电的CoWoS,Intel的Foveros,现在三星也公布了自家的3D封装技术X-Cube。显而易见的是,未来我们买到的电子产品中,使用3D封装技术的芯片比例会越来越高。

(素材:chinaaet.如涉版权请联系删除)

(素材:chinaaet.如涉版权请联系删除)

上一篇:滤波器和模拟输出缓谐波失真系数

上一篇:三块控制器的控制芯片管脚功能

公网安备44030402000607

公网安备44030402000607