数控振荡器集成带宽线性度性能

发布时间:2020/9/19 22:13:44 访问次数:929

DDS独立集成电路的最大供应商,可能也是最独特的供应商,而当前的数控振荡器(NCO)往往都集成到AD9164 或AD9174 之类RF DAC中。虽然这些器件在多GHz带宽上具备出色的噪声和线性度性能,但它们都不适合测试中等速度、高分辨率ADC,例如LTC2378-20 、AD4020 或AD7768 。

基于IEEE 1241标准的典型ADC(ac)测试设置的处理链。DDFS能够让整个测量系统完全实现数字化,具备多种优势,包括完全的灵活性和相干取样采集.

用于计算正弦近似值的多项式方法允许使用成本极低的通用DSP,在复杂性与精度之间达成了不错的平衡。多项式级数展开也很有吸引力,因为它相对简单,并且能够采用选择的幂级数类型提供充分的灵活性,并且调整算法来实现给定精度。它不需要很大的存储空间(可能不到100行SHARC DSP汇编代码),只需要几个RAM位置来存储多项式系数和变量,因为正弦值只在采样时刻计算。

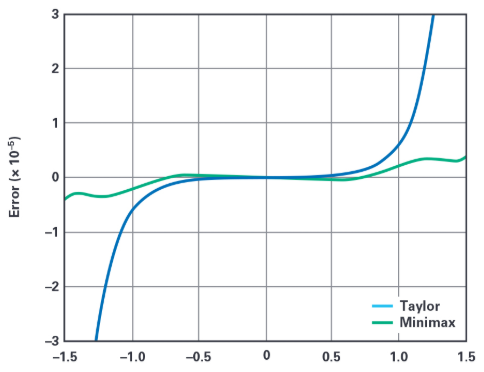

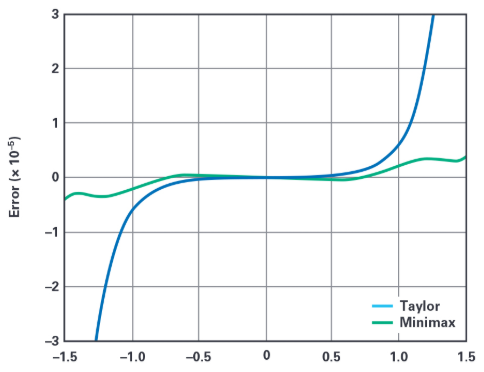

正弦近似值函数,显然会选择使用具有适当顺序的泰勒/麦克劳林幂级数来满足目标精度。但是,由于幂级数在端点处往往会失效,所以在执行任何多项式求值之前,必须将参数输入范围缩小到更小的区间。

如果不缩小参数范围,只能使用非常高阶的多项式来支持在功能域(例如[-π, +π])中实现高精度。所以,需要对初等函数进行一些变换,以获取所需的约化参数,例如sin(|x|) = sin(f + k × π/2)和sin(f) = sin(x - k × π/2),其中0 ≤f<π/2。对于三角函数,要特别注意不要使用减法相消,以免严重降低精度,并导致灾难性后果,特别是在运算精度极差的情况下。在我们的例子中,当相位输入大于或接近π/2的整数倍数时,会发生这种情况。

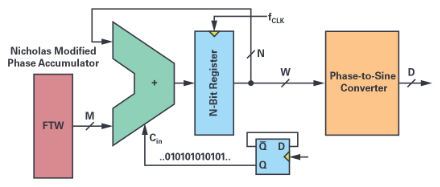

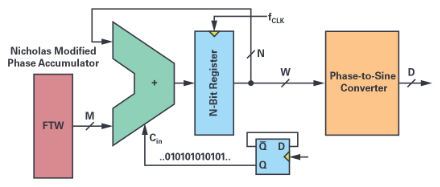

架构实现的实际正弦波形生成器,主要是相位-幅度转换模块不同,受数字无线电应用这一市场导向影响,该模块通常针对速度和功耗,而不是高精度而优化。实施相位-正弦幅度转换器最简单的方法就是使用ROM,采用一对一映射的方式来存储正弦值。

LUT的长度与相位累加器的宽度N呈指数增长(2N),并且与波表数据字精度W呈线性增长。而且,减小累加器的尺寸或截断其输出之间的权衡和取舍会导致频率分辨率降低,并且严重降低SFDR的性能。

相位或幅度量化导致的杂散会降低-6 dB/位。实现精细的频率调谐通常需要较大的N,已有几种技术可用来限制ROM的尺寸,同时保持足够的杂散性能。一般会使用简单的压缩方法,利用正弦或余弦函数的四分之一波长对称性将相位幅度范围减小4倍。为了进一步缩小范围,实际会使用截断相位累加器输出的方法,不过这会导致产生杂散谐波。

(素材:chinaaet.如涉版权请联系删除)

DDS独立集成电路的最大供应商,可能也是最独特的供应商,而当前的数控振荡器(NCO)往往都集成到AD9164 或AD9174 之类RF DAC中。虽然这些器件在多GHz带宽上具备出色的噪声和线性度性能,但它们都不适合测试中等速度、高分辨率ADC,例如LTC2378-20 、AD4020 或AD7768 。

基于IEEE 1241标准的典型ADC(ac)测试设置的处理链。DDFS能够让整个测量系统完全实现数字化,具备多种优势,包括完全的灵活性和相干取样采集.

用于计算正弦近似值的多项式方法允许使用成本极低的通用DSP,在复杂性与精度之间达成了不错的平衡。多项式级数展开也很有吸引力,因为它相对简单,并且能够采用选择的幂级数类型提供充分的灵活性,并且调整算法来实现给定精度。它不需要很大的存储空间(可能不到100行SHARC DSP汇编代码),只需要几个RAM位置来存储多项式系数和变量,因为正弦值只在采样时刻计算。

正弦近似值函数,显然会选择使用具有适当顺序的泰勒/麦克劳林幂级数来满足目标精度。但是,由于幂级数在端点处往往会失效,所以在执行任何多项式求值之前,必须将参数输入范围缩小到更小的区间。

如果不缩小参数范围,只能使用非常高阶的多项式来支持在功能域(例如[-π, +π])中实现高精度。所以,需要对初等函数进行一些变换,以获取所需的约化参数,例如sin(|x|) = sin(f + k × π/2)和sin(f) = sin(x - k × π/2),其中0 ≤f<π/2。对于三角函数,要特别注意不要使用减法相消,以免严重降低精度,并导致灾难性后果,特别是在运算精度极差的情况下。在我们的例子中,当相位输入大于或接近π/2的整数倍数时,会发生这种情况。

架构实现的实际正弦波形生成器,主要是相位-幅度转换模块不同,受数字无线电应用这一市场导向影响,该模块通常针对速度和功耗,而不是高精度而优化。实施相位-正弦幅度转换器最简单的方法就是使用ROM,采用一对一映射的方式来存储正弦值。

LUT的长度与相位累加器的宽度N呈指数增长(2N),并且与波表数据字精度W呈线性增长。而且,减小累加器的尺寸或截断其输出之间的权衡和取舍会导致频率分辨率降低,并且严重降低SFDR的性能。

相位或幅度量化导致的杂散会降低-6 dB/位。实现精细的频率调谐通常需要较大的N,已有几种技术可用来限制ROM的尺寸,同时保持足够的杂散性能。一般会使用简单的压缩方法,利用正弦或余弦函数的四分之一波长对称性将相位幅度范围减小4倍。为了进一步缩小范围,实际会使用截断相位累加器输出的方法,不过这会导致产生杂散谐波。

(素材:chinaaet.如涉版权请联系删除)

上一篇:累加器寄存器的电流相位

上一篇:高精度交流信号振荡器的音频频谱

热门点击

热门点击

- 恒流驱动电路调节输出电流

- 控制七段共阴极数码管显示电路

- 高压绝缘方法的栅极驱动器

- 16uA的小待机电流和CoolCLOCK技术

- 模块中时序控制器高效率电源管理

- 高压MOS管功率开关的原边控制开关电源

- 600V栅极驱动器低压差稳压器

- 微型晶圆级芯片封装的低IQ负载开关和LDO稳

- 增强性能并与分立组件

- 滤波器和模拟输出缓谐波失真系数

推荐技术资料

推荐技术资料

- 自制智能型ICL7135

- 表头使ff11CL7135作为ADC,ICL7135是... [详细]

公网安备44030402000607

公网安备44030402000607