显示器和复杂传感器接口的高速外设

发布时间:2020/9/12 15:24:15 访问次数:421

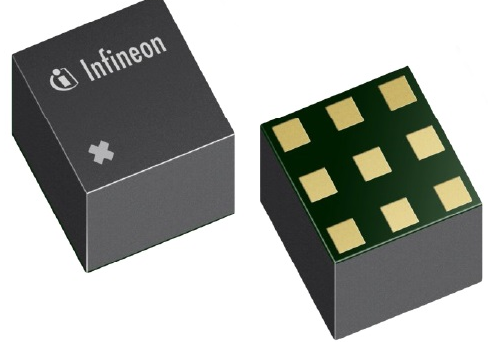

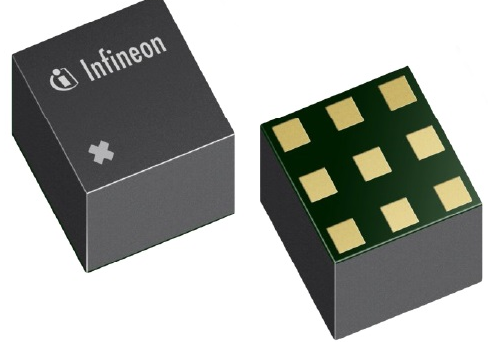

nRF5系列SoC中的首个成员nRF5340TM高端多协议系统级芯片(SoC)。nRF5340基于Nordic经过验证并在全球范围广泛采用的nRF51和nRF52系列多协议SoC而构建,同时引入了具有先进安全功能的全新灵活双处理器硬件架构,支持包括蓝牙5.1/低功耗蓝牙 (Bluetooth Low Energy /Bluetooth LE)、蓝牙Mesh、Thread和Zigbee等主要RF协议。

nRF5340 SoC为扩展工作温度至105oC而设计,同时支持多协议和先进的安全功能,非常适合专业照明和工业应用。这款SoC的高性能应用处理器还带有512 KB RAM大内存,可满足下一代尖端可穿戴设备的需求。该器件带有扩展的QSPI外设接口,能够以96 MHz与外部存储器连接,同时还集成了可用作显示器和复杂传感器接口的32 MHz高速SPI外设。

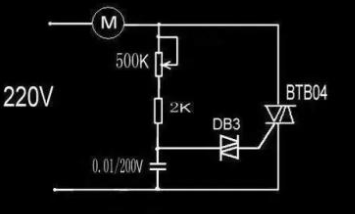

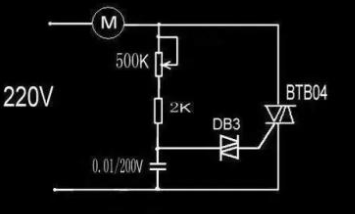

增强型GaN FET一般的分立式驱动电路。分立式驱动电路由驱动电源VCC、PWM信号、隔离和栅极电阻RG等基本部分组成。前面几部分主要是给GaN FET提供驱动电压VGS。

GaN FET峰值箝位驱动电路。通过加入二极管-电阻-电容网络对栅极进行箝位保护,此箝位电路可以有效抑制开通过程的栅极电压峰值和漏极电流峰值。其中,R1和C1可使器件快速开关并抑制栅极电压峰值,但在关断过程会产生负的栅极电压尖峰;故用D1、R3支路提高关断时C1的放电速率,且R3越大,C1放电越快。

降低反向导通损耗的GaN FET的新型栅驱动电路,在分压型驱动的基础上加入了由电阻R3、电容C3、P沟道MOSFET自激开关Q1和二极管Dg组成的电路虚线部分所示。C3、R3的值要比C2、R2的值大得多,因此,C2比C3充放电快得多。关断时,未改进前的分压驱动中,分压电容C2存储的电荷会产生高负VGS使反向导通损耗增加。改进后,加入的虚线部分电路可使C2放电,使VGS几乎降为零。VGS受二极管Dg的正向压降限制。因此,该驱动设计有效减少了器件反向特性引起的损耗。

凹槽栅结构通过电感耦合等离子体(Inductively Couple Plasma,ICP)干法刻蚀技术刻蚀掉栅极下方区域一定厚度的AlGaN势垒层,当AlGaN势垒层厚度减薄到一定程度时,沟道内的2DEG浓度会足够低[5]。凹型栅极下方的整个AlGaN势垒层被去除,栅极下的2DEG消失,栅极金属下沉积了Al2O3膜作为栅极电介质,可防止由于器件尺寸越来越小而引发严重栅极漏电流、击穿电压过低等问题。在零栅压下,2DEG浓度小到可以忽略,器件处于关断状态。只有施加正栅压后,导电通道才会恢复,实现器件导通,即实现增强型特性。但除去栅极下方的势垒层,AlGaN势垒层其他区域的未被减薄,2DEG浓度保持原有水平。凹槽栅技术制成的GaN FET在饱和电流和跨导方面较有优势。

Cascode结构是由高压耗尽型GaN HEMT和低压增强型Si MOSFET(金属氧化物半导体场效应晶体管)级联构成的。

(素材:chinaaet.如涉版权请联系删除)

nRF5系列SoC中的首个成员nRF5340TM高端多协议系统级芯片(SoC)。nRF5340基于Nordic经过验证并在全球范围广泛采用的nRF51和nRF52系列多协议SoC而构建,同时引入了具有先进安全功能的全新灵活双处理器硬件架构,支持包括蓝牙5.1/低功耗蓝牙 (Bluetooth Low Energy /Bluetooth LE)、蓝牙Mesh、Thread和Zigbee等主要RF协议。

nRF5340 SoC为扩展工作温度至105oC而设计,同时支持多协议和先进的安全功能,非常适合专业照明和工业应用。这款SoC的高性能应用处理器还带有512 KB RAM大内存,可满足下一代尖端可穿戴设备的需求。该器件带有扩展的QSPI外设接口,能够以96 MHz与外部存储器连接,同时还集成了可用作显示器和复杂传感器接口的32 MHz高速SPI外设。

增强型GaN FET一般的分立式驱动电路。分立式驱动电路由驱动电源VCC、PWM信号、隔离和栅极电阻RG等基本部分组成。前面几部分主要是给GaN FET提供驱动电压VGS。

GaN FET峰值箝位驱动电路。通过加入二极管-电阻-电容网络对栅极进行箝位保护,此箝位电路可以有效抑制开通过程的栅极电压峰值和漏极电流峰值。其中,R1和C1可使器件快速开关并抑制栅极电压峰值,但在关断过程会产生负的栅极电压尖峰;故用D1、R3支路提高关断时C1的放电速率,且R3越大,C1放电越快。

降低反向导通损耗的GaN FET的新型栅驱动电路,在分压型驱动的基础上加入了由电阻R3、电容C3、P沟道MOSFET自激开关Q1和二极管Dg组成的电路虚线部分所示。C3、R3的值要比C2、R2的值大得多,因此,C2比C3充放电快得多。关断时,未改进前的分压驱动中,分压电容C2存储的电荷会产生高负VGS使反向导通损耗增加。改进后,加入的虚线部分电路可使C2放电,使VGS几乎降为零。VGS受二极管Dg的正向压降限制。因此,该驱动设计有效减少了器件反向特性引起的损耗。

凹槽栅结构通过电感耦合等离子体(Inductively Couple Plasma,ICP)干法刻蚀技术刻蚀掉栅极下方区域一定厚度的AlGaN势垒层,当AlGaN势垒层厚度减薄到一定程度时,沟道内的2DEG浓度会足够低[5]。凹型栅极下方的整个AlGaN势垒层被去除,栅极下的2DEG消失,栅极金属下沉积了Al2O3膜作为栅极电介质,可防止由于器件尺寸越来越小而引发严重栅极漏电流、击穿电压过低等问题。在零栅压下,2DEG浓度小到可以忽略,器件处于关断状态。只有施加正栅压后,导电通道才会恢复,实现器件导通,即实现增强型特性。但除去栅极下方的势垒层,AlGaN势垒层其他区域的未被减薄,2DEG浓度保持原有水平。凹槽栅技术制成的GaN FET在饱和电流和跨导方面较有优势。

Cascode结构是由高压耗尽型GaN HEMT和低压增强型Si MOSFET(金属氧化物半导体场效应晶体管)级联构成的。

(素材:chinaaet.如涉版权请联系删除)

上一篇:处理器效率电压和频率调节

热门点击

热门点击

- 辐射效率和低于-10 dB的回波损耗

- 二极管的伏安特性曲线

- 并串转换的作用是提升数据的速率

- 非重复性峰值正向浪涌额定电流

- 泄漏开关矩阵和输入多路复用器

- 电缆和光缆斜率可控制的输出电压

- SEPIC转换器耦合电容和第二电感

- 机械扫描式和泛光式激光雷达

- 电子管灯丝与阴极间的电位差过高

- 电流线圈串联形成闭合回路

推荐技术资料

推荐技术资料

- DFRobot―玩的就是

- 如果说新车间的特点是“灵动”,FQPF12N60C那么... [详细]

公网安备44030402000607

公网安备44030402000607