抗辐射加固逻辑芯片的两倍以上实现对双口RAM控制器的功能

发布时间:2023/5/9 9:00:31 访问次数:78

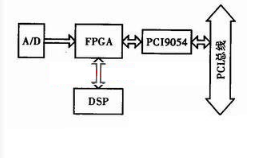

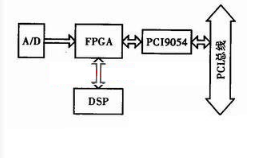

PCI9054与本地总线之间的接口称之为LOCAL BUS,是CPCI总线系统设计中十分重要的一环。PCI9054 LOCAL BUS在系统设计中,其总线直接与Alter公司的EP2S90F78014芯片的数据总线相连,同时通过运用Verilog HDL语言编程来实现对双口RAM控制器的功能。

PCI9054 LOCAL BUS有3种工作模式,分别为M、J和C模式。M模式是专为Motorola公司开发和设计的,而另外两种工作模式就应用的比较广泛。其中J模式因为没有LocaL Master,所以它的地址总线和数据线没有分开,从而增加了开发难度。而在C模式下,PCI9054芯片通过片内的逻辑控制可以将CPCI的局部地址和数据总线分开,从而有效地降低了开发难度,并且能灵活地为本地工作时序提供各种工作方式,设计方案选择了LOCAL总线的C工作模式,工作频率为40 MHz。

福建芯鸿科技有限公司http://xhkjgs.51dzw.com

QML-V标准认证的RHFOSC04 (SMD 5962F20207)晶振驱动器/分频器芯片和RHFAHC00 (SMD 5962F18202)四路NAND门逻辑芯片的门工作速度是典型抗辐射加固逻辑芯片的两倍以上,保证高频电路响应速度更快。

采用意法半导体专有的经过整个航天工业检验的130nm CMOS技术设计,新器件兼备高工作速度、低工作电流和业内一流的高达 300 krad (Si) TID的RHA(抗辐射加固保证)级别的抗辐射能力,在125 MeV.cm2/mg下无SEL 和 SET[3]现象发生。

其1.8V至3.6V的电源电压有助于满足典型卫星和太空飞行器机载设备对功耗和能耗的严格限制。

RHFOSC04兼有多个分立逻辑器件的作用,可直接驱动晶体振荡器,简化时钟电路设计并提高电路稳定性,同时节省电路板空间,并提高系统可靠性。分频器提供标称频率、2分频、4分频和8分频输出,增加了时钟分频的灵活性。

新器件交付方式有裸片和封装芯片两种,裸片可以直接集成在客户应用设计的系统级封装(SiP)内,封装芯片采用陶瓷密封Flat 14 (RHFAHC00)和Flat 10 (RHFOSC04)。

PCI9054支持主模式、从模式和DMA传输方式,根据本系统设计的需求,采用从模式传输方式,即允许CPCI总线上的主设备访问局部总线上的配置寄存器或内存,支持多种模式传输。

FPGA内部逻辑要设计本地端总线控制模块,实现局部总线的状态控制,同时产生片内的读写时序及地址信号以支持突发传输和单周期传输,因此使用Verilog HDL语言中的状态机来完成上述功能。其状态转换。

以PCI9054为核心介绍了CPCI板卡与嵌入式CPU板卡之间高速数据通信系统接口的软硬件设计。PCI9054因其灵活和方便的接口功能,使操作者只需关心LOCAL BUS接口电路的时序设计,并且利用其传输速率高的特性,对实时性要求较高的系统解决其传输数据的问题。

(素材:21ic.如涉版权请联系删除)

PCI9054与本地总线之间的接口称之为LOCAL BUS,是CPCI总线系统设计中十分重要的一环。PCI9054 LOCAL BUS在系统设计中,其总线直接与Alter公司的EP2S90F78014芯片的数据总线相连,同时通过运用Verilog HDL语言编程来实现对双口RAM控制器的功能。

PCI9054 LOCAL BUS有3种工作模式,分别为M、J和C模式。M模式是专为Motorola公司开发和设计的,而另外两种工作模式就应用的比较广泛。其中J模式因为没有LocaL Master,所以它的地址总线和数据线没有分开,从而增加了开发难度。而在C模式下,PCI9054芯片通过片内的逻辑控制可以将CPCI的局部地址和数据总线分开,从而有效地降低了开发难度,并且能灵活地为本地工作时序提供各种工作方式,设计方案选择了LOCAL总线的C工作模式,工作频率为40 MHz。

福建芯鸿科技有限公司http://xhkjgs.51dzw.com

QML-V标准认证的RHFOSC04 (SMD 5962F20207)晶振驱动器/分频器芯片和RHFAHC00 (SMD 5962F18202)四路NAND门逻辑芯片的门工作速度是典型抗辐射加固逻辑芯片的两倍以上,保证高频电路响应速度更快。

采用意法半导体专有的经过整个航天工业检验的130nm CMOS技术设计,新器件兼备高工作速度、低工作电流和业内一流的高达 300 krad (Si) TID的RHA(抗辐射加固保证)级别的抗辐射能力,在125 MeV.cm2/mg下无SEL 和 SET[3]现象发生。

其1.8V至3.6V的电源电压有助于满足典型卫星和太空飞行器机载设备对功耗和能耗的严格限制。

RHFOSC04兼有多个分立逻辑器件的作用,可直接驱动晶体振荡器,简化时钟电路设计并提高电路稳定性,同时节省电路板空间,并提高系统可靠性。分频器提供标称频率、2分频、4分频和8分频输出,增加了时钟分频的灵活性。

新器件交付方式有裸片和封装芯片两种,裸片可以直接集成在客户应用设计的系统级封装(SiP)内,封装芯片采用陶瓷密封Flat 14 (RHFAHC00)和Flat 10 (RHFOSC04)。

PCI9054支持主模式、从模式和DMA传输方式,根据本系统设计的需求,采用从模式传输方式,即允许CPCI总线上的主设备访问局部总线上的配置寄存器或内存,支持多种模式传输。

FPGA内部逻辑要设计本地端总线控制模块,实现局部总线的状态控制,同时产生片内的读写时序及地址信号以支持突发传输和单周期传输,因此使用Verilog HDL语言中的状态机来完成上述功能。其状态转换。

以PCI9054为核心介绍了CPCI板卡与嵌入式CPU板卡之间高速数据通信系统接口的软硬件设计。PCI9054因其灵活和方便的接口功能,使操作者只需关心LOCAL BUS接口电路的时序设计,并且利用其传输速率高的特性,对实时性要求较高的系统解决其传输数据的问题。

(素材:21ic.如涉版权请联系删除)

上一篇:扭矩无线传感器的种类

公网安备44030402000607

公网安备44030402000607