P17C8150MA-33屏蔽体对电磁能流的反射

发布时间:2019/11/4 20:52:02 访问次数:1016

P17C8150MA-33抗干扰能力就越差。如果受干扰的敏感设各不只一个,应该选择敏感度最高的敏感设各为代表,以建立受干扰者的模式。

屏蔽、接地与滤波,电磁兼容的技术关键在于有效地抑制电磁干扰,只有掌握电磁干扰的抑制技术,并在系统或设备的设计、生产、使用以及维修过程中合理地应用,才能实现电磁兼容。因此,干扰的抑制技术是电磁兼容领域的重要课题。抑制干扰的方法很多,屏蔽、接地和滤波是常用的方法。

电磁屏蔽,抑制以场的形式造成干扰的有效方法是电磁屏蔽,所谓电磁屏蔽就是以某种材料(导电的或导磁的材料)制成的屏蔽壳体(实体的或非实体的),将需要屏蔽的区域封闭起来,形成电磁隔离,即其内的电磁场不能越出这一区域,而外来的辐射电磁场不能进入这一区域(或者进出该区域的电磁能量将受到很大的衰减)。

电磁屏蔽的作用原理是利用屏蔽体对电磁能流的反射、吸收和引导作用。而这些作用是与屏蔽结构表面上和屏蔽体内感生的电荷、电流与极化现象密切相关。按屏蔽原理,可分为电场屏蔽、磁场屏蔽和电磁场屏蔽,下面阐述各种屏蔽的工作原理。

电场屏蔽简称电屏蔽,实质是减少设备(或电路、组件、元件)间的电场感应,它包括静电屏蔽和交变电场(例如高阻抗电场源的近场)的屏蔽。

静电屏蔽,根据电磁场理论可知,置于静电场中的导体在静电平衡的条件下,有下列性质:

导体内部任何一点的电场为零; '

导体表面上任何一点的电场方向与该点的导体表面垂直;

整个导体是一个等位体;

导体内部没有静电荷存在,电荷只能分布在导体的表面上。

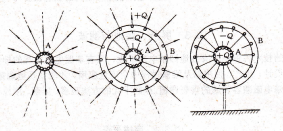

即使其内部存在空腔的导体,在静电场中也有上述性质。因此,如果把有空腔的导体引入电场,由于导体的内表面无净电荷,空腔空间中也无电场,所以该导体起了隔绝外电场的作用,使外电场对空腔空间并无影响。反之,如果把导体接地,即使空腔内有带电体产生电场,在腔体外面也无电场。这就是静电屏蔽的理论根据。例如,当屏蔽内空腔存在正电荷Q时,见图10一4(b)所示,屏蔽体内侧感应出等量的负电荷,外侧感应出等量的正电荷。从图10-4可以看出,仅用屏蔽体将静电场源包围起来,实际上起不到屏蔽作用。只有将屏蔽体接地时,如图10一4(c)所示,才能将静电场源所产生的电力线封闭在屏蔽体内部,屏蔽体才能真正起到屏蔽的作用。

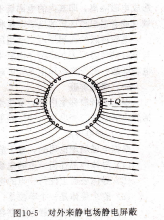

当屏蔽体外有静电场的干扰时,由于导体为等位体,那么其屏蔽体内部空间不会出现电力线,即屏蔽体内部不存在电场,从而实现静电屏蔽。而屏蔽体之外有电力线,存在并终止在屏蔽体上,如图10-5所示。在电力线的端点有面电荷出现于屏蔽体的外表面,在屏蔽体的内侧出现等量反号的电荷,而屏蔽体内部没有电荷。当屏蔽体完全封闭时,不管该屏蔽体对电荷的静电屏蔽(a)孤立导体A;(b)导体B包围的情况;(c)静电屏蔽。

是否接地,屏蔽体内部的外电场均为零。但实际上屏蔽体是不可能完全封闭的,若不接地,就会引起电力线侵入,造成直接或间接的静电耦合。为防止这种现象,此时屏蔽体仍需接地。

交变电场的屏蔽,对于交变电场的屏蔽原理,采用电路理论加以解释较为方便,因为干扰源与感受器之间的电场感应可用分布电容来进行描述。

如图10-6所示,设干扰源g上有一交变电压魄,在其附近有一受感器s通过阻抗zs接地,干扰源g对受感器s的电场感应作用等效为分布电容Ci的耦合,从而形成了由魄、Cj、zg和zs构成的耦合回路,在受感器上产生的干扰机为

us=jwcjzsug/1+jwcj(zg+zs) (10-1)

从式中可以看出,分布电容Cj越大,则受感器受到的干扰电压越大。为了减小干扰,可使干扰源与受感器尽量远离,当无法满足要求时,则要采用屏蔽。

为了减小g对s的干扰,在两者之间加入屏蔽体,如图10-7所示,使得原来的电容Cj变为CI、Cl串联与Cl的并联。由于Cl较小,故可忽略,得屏蔽体被感应的电压为

uj=1+jwcjzjug/1+jwcj(zg+zj) (10-2)

受感器上被感应的电压为

us=jwcjzsuj/1+jwCj(zi+zs) (10-3)

从上面两式可以看出,要使|us|比较小,zj应比较小,而zj为屏蔽体的阻抗和接地阻抗之和。为此,屏蔽体必须选用导电性能好的材料,而且必须良好地接地,只有这样才能有效地减少干扰。一般情况下,要求接地阻抗小于2mΩ,比较严格的场合要求小于0.5 mΩ。若屏蔽对外来静电场静电屏蔽,异步二进制计数器的原理、结构简单,因各触发器不是同时翻转,而是逐级脉动翻转实现计数进位的,故亦称为纹波计数器①。图6.5.9中的虚线是考虑了触发器逐级翻转中平均传输延迟时间rpd的波形。由于各触发器的翻转时间有延迟,若用该计数器驱动组合逻辑电路,则可能出现瞬间逻辑错误。例如,当计数值从0111加1时,先后要经过0110、0100、0000几个状态,才最终翻转为1000。如果对0110、0100、0000译码,这时译码输出端则会出现毛刺状波形。另外,当计数脉冲频率很高时,03~0。甚至会出现编码输出分辨不清的情况。对于一个Ⅳ位二进制异步计数器来说,从一个计数脉冲开始作用到第一个触发器,到第Ⅳ个触发器翻转达到稳定状态,需要经历的时间为rrpd。为了保证正确地检出计数器的输出状态,必须满足rcP>>助pd的条件,其中,rcP为计数脉冲CP的周期。

典型集成电路中规模集成电路74HC/HCT393中集成了两个如图6.5.8所示的4位异步二进制计数器,图6.5.10所示是它的引脚图。在5Ⅴ、25℃工作条件下,74HC/HCT393中每级触发器传输延迟时间的典型值为6 ns。

同步二进制加计数器,为了提高计数速度,可采用同步计数器。其特点是,计数脉冲作为时钟信号同时接于各位触发器的时图6.5.10 74HC/HCT393钟脉冲输入端,在每次时钟脉冲沿到来之前,根据当的引脚图前计数器状态,利用组合逻辑控制,准各好适当的条件。当计数脉冲沿到来时,所有应翻转的触发器同时翻转,同时也使所有应保若干典型的时序逻辑集成电路.

P17C8150MA-33抗干扰能力就越差。如果受干扰的敏感设各不只一个,应该选择敏感度最高的敏感设各为代表,以建立受干扰者的模式。

屏蔽、接地与滤波,电磁兼容的技术关键在于有效地抑制电磁干扰,只有掌握电磁干扰的抑制技术,并在系统或设备的设计、生产、使用以及维修过程中合理地应用,才能实现电磁兼容。因此,干扰的抑制技术是电磁兼容领域的重要课题。抑制干扰的方法很多,屏蔽、接地和滤波是常用的方法。

电磁屏蔽,抑制以场的形式造成干扰的有效方法是电磁屏蔽,所谓电磁屏蔽就是以某种材料(导电的或导磁的材料)制成的屏蔽壳体(实体的或非实体的),将需要屏蔽的区域封闭起来,形成电磁隔离,即其内的电磁场不能越出这一区域,而外来的辐射电磁场不能进入这一区域(或者进出该区域的电磁能量将受到很大的衰减)。

电磁屏蔽的作用原理是利用屏蔽体对电磁能流的反射、吸收和引导作用。而这些作用是与屏蔽结构表面上和屏蔽体内感生的电荷、电流与极化现象密切相关。按屏蔽原理,可分为电场屏蔽、磁场屏蔽和电磁场屏蔽,下面阐述各种屏蔽的工作原理。

电场屏蔽简称电屏蔽,实质是减少设备(或电路、组件、元件)间的电场感应,它包括静电屏蔽和交变电场(例如高阻抗电场源的近场)的屏蔽。

静电屏蔽,根据电磁场理论可知,置于静电场中的导体在静电平衡的条件下,有下列性质:

导体内部任何一点的电场为零; '

导体表面上任何一点的电场方向与该点的导体表面垂直;

整个导体是一个等位体;

导体内部没有静电荷存在,电荷只能分布在导体的表面上。

即使其内部存在空腔的导体,在静电场中也有上述性质。因此,如果把有空腔的导体引入电场,由于导体的内表面无净电荷,空腔空间中也无电场,所以该导体起了隔绝外电场的作用,使外电场对空腔空间并无影响。反之,如果把导体接地,即使空腔内有带电体产生电场,在腔体外面也无电场。这就是静电屏蔽的理论根据。例如,当屏蔽内空腔存在正电荷Q时,见图10一4(b)所示,屏蔽体内侧感应出等量的负电荷,外侧感应出等量的正电荷。从图10-4可以看出,仅用屏蔽体将静电场源包围起来,实际上起不到屏蔽作用。只有将屏蔽体接地时,如图10一4(c)所示,才能将静电场源所产生的电力线封闭在屏蔽体内部,屏蔽体才能真正起到屏蔽的作用。

当屏蔽体外有静电场的干扰时,由于导体为等位体,那么其屏蔽体内部空间不会出现电力线,即屏蔽体内部不存在电场,从而实现静电屏蔽。而屏蔽体之外有电力线,存在并终止在屏蔽体上,如图10-5所示。在电力线的端点有面电荷出现于屏蔽体的外表面,在屏蔽体的内侧出现等量反号的电荷,而屏蔽体内部没有电荷。当屏蔽体完全封闭时,不管该屏蔽体对电荷的静电屏蔽(a)孤立导体A;(b)导体B包围的情况;(c)静电屏蔽。

是否接地,屏蔽体内部的外电场均为零。但实际上屏蔽体是不可能完全封闭的,若不接地,就会引起电力线侵入,造成直接或间接的静电耦合。为防止这种现象,此时屏蔽体仍需接地。

交变电场的屏蔽,对于交变电场的屏蔽原理,采用电路理论加以解释较为方便,因为干扰源与感受器之间的电场感应可用分布电容来进行描述。

如图10-6所示,设干扰源g上有一交变电压魄,在其附近有一受感器s通过阻抗zs接地,干扰源g对受感器s的电场感应作用等效为分布电容Ci的耦合,从而形成了由魄、Cj、zg和zs构成的耦合回路,在受感器上产生的干扰机为

us=jwcjzsug/1+jwcj(zg+zs) (10-1)

从式中可以看出,分布电容Cj越大,则受感器受到的干扰电压越大。为了减小干扰,可使干扰源与受感器尽量远离,当无法满足要求时,则要采用屏蔽。

为了减小g对s的干扰,在两者之间加入屏蔽体,如图10-7所示,使得原来的电容Cj变为CI、Cl串联与Cl的并联。由于Cl较小,故可忽略,得屏蔽体被感应的电压为

uj=1+jwcjzjug/1+jwcj(zg+zj) (10-2)

受感器上被感应的电压为

us=jwcjzsuj/1+jwCj(zi+zs) (10-3)

从上面两式可以看出,要使|us|比较小,zj应比较小,而zj为屏蔽体的阻抗和接地阻抗之和。为此,屏蔽体必须选用导电性能好的材料,而且必须良好地接地,只有这样才能有效地减少干扰。一般情况下,要求接地阻抗小于2mΩ,比较严格的场合要求小于0.5 mΩ。若屏蔽对外来静电场静电屏蔽,异步二进制计数器的原理、结构简单,因各触发器不是同时翻转,而是逐级脉动翻转实现计数进位的,故亦称为纹波计数器①。图6.5.9中的虚线是考虑了触发器逐级翻转中平均传输延迟时间rpd的波形。由于各触发器的翻转时间有延迟,若用该计数器驱动组合逻辑电路,则可能出现瞬间逻辑错误。例如,当计数值从0111加1时,先后要经过0110、0100、0000几个状态,才最终翻转为1000。如果对0110、0100、0000译码,这时译码输出端则会出现毛刺状波形。另外,当计数脉冲频率很高时,03~0。甚至会出现编码输出分辨不清的情况。对于一个Ⅳ位二进制异步计数器来说,从一个计数脉冲开始作用到第一个触发器,到第Ⅳ个触发器翻转达到稳定状态,需要经历的时间为rrpd。为了保证正确地检出计数器的输出状态,必须满足rcP>>助pd的条件,其中,rcP为计数脉冲CP的周期。

典型集成电路中规模集成电路74HC/HCT393中集成了两个如图6.5.8所示的4位异步二进制计数器,图6.5.10所示是它的引脚图。在5Ⅴ、25℃工作条件下,74HC/HCT393中每级触发器传输延迟时间的典型值为6 ns。

同步二进制加计数器,为了提高计数速度,可采用同步计数器。其特点是,计数脉冲作为时钟信号同时接于各位触发器的时图6.5.10 74HC/HCT393钟脉冲输入端,在每次时钟脉冲沿到来之前,根据当的引脚图前计数器状态,利用组合逻辑控制,准各好适当的条件。当计数脉冲沿到来时,所有应翻转的触发器同时翻转,同时也使所有应保若干典型的时序逻辑集成电路.

公网安备44030402000607

公网安备44030402000607