SN74LVC244APW设计控制单元电路

发布时间:2019/10/25 18:02:12 访问次数:1120

SN74LVC244APW下一个时钟到来时,再回到s1状态接受下一个数码。控制单元有多个输出,状态图中标出输出变量的,在该状态下为1,其余情况下各个输出均为0。例如在S3状态,CⅣr为1,其余输出均为0。

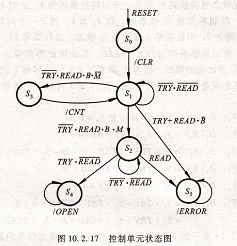

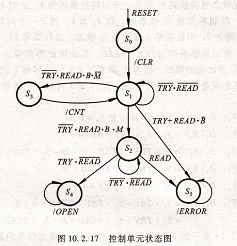

图10.2.16所示控制单元ASM图的硬件实现,采用一个触发器对应一个状态的方法。用六个D触发器FF。~FF5的输出表示s0~S5六种状态,开锁过程中的每一时刻,只能有一个状态为1,其余状态为0。根据图10,2.17所示的状态图,可以列出控制单元的状态转换表,如表10.2.3所示。以次态是s1状态为例说明列表过程。在图10,2.17中有三个箭头(s。状态、S3状态和S1状态本身)最终直接指向s1状态框,说明控制单元在sO、S1和S3状态下,根据不同的转换条件作用,可以转换到s1状态。例如控制单元现态为SO,此时FF。为1,其余触发器均为0。在下一个时钟脉冲来到时,不需要其他任何条件,控制单元状态将转换到Sl状态,所以转换条件为1,此时FFl为1,其余触发器为0;控制单元在Sl状态时,则s1为1,当下一个时钟脉冲来到时,rRy和READ均为0,则控制单元保持在S1状态,这样要求FF1的输入为s1・TRy・READ,所以转换条件为「Ry・RDD。其余依此类推得出表10.2.3。表中没有列出s。为次态的情况,因为S。是直接由复位信号建立的,另外为方便起见,没有区别现态和次态的符号。由表10,2.3可以写出各触发器的输入逻辑关系式

FF0: DO=0 (reset异步置sO=1)

FFl: D1(s1)=s0+s1・rRy・ReAD+S3

FF2: D2(S2)=s1・rRy・READ・B・nf+s2・rRy・READ

FF3: D3(S3)=s1・rRy・READ・B・M

FF4: D4(s4)=S2・READ・TRy+s4

FF5: D5(S5)=s1・rRy+s1・rRy.READ・B+s2・READ+S5

=s1.rRy+s1・READ・B+s2・READ+S5

由图10.2.16所示的ASM图可以写出控制单元输出信号的逻辑表达式

CLR=S0 (低电平有效)

CⅣT=s3

0PEⅣ=S4

ERROR=S5

根据上述逻辑方程得出数字锁的控制单元电路如图10.2.18所示。图10.2.15所示为处理单元电路的结构图。如果D触发器选用74HC74。多路选择器选用74HC151,比较器选用74HC85,计数器选用74HC163,外加必要的门电路,将控制单元和处理单元组合起来就可以构成数字密码锁系统,数字锁系统电路图略。

比较两种控制单元的硬仵实现方法可知,触发器状态组合方法所用的触发器少,但组合电路相对复杂。一个触发器对应一个状态所用的触发器较多,但可以简化组合电路。对于寄存器数量多,而逻辑门相对缺乏的FPGA器件,采用后一种方法可以提高器件资源的利用率,提高电路的速度和可靠性。

SN74LVC244APW下一个时钟到来时,再回到s1状态接受下一个数码。控制单元有多个输出,状态图中标出输出变量的,在该状态下为1,其余情况下各个输出均为0。例如在S3状态,CⅣr为1,其余输出均为0。

图10.2.16所示控制单元ASM图的硬件实现,采用一个触发器对应一个状态的方法。用六个D触发器FF。~FF5的输出表示s0~S5六种状态,开锁过程中的每一时刻,只能有一个状态为1,其余状态为0。根据图10,2.17所示的状态图,可以列出控制单元的状态转换表,如表10.2.3所示。以次态是s1状态为例说明列表过程。在图10,2.17中有三个箭头(s。状态、S3状态和S1状态本身)最终直接指向s1状态框,说明控制单元在sO、S1和S3状态下,根据不同的转换条件作用,可以转换到s1状态。例如控制单元现态为SO,此时FF。为1,其余触发器均为0。在下一个时钟脉冲来到时,不需要其他任何条件,控制单元状态将转换到Sl状态,所以转换条件为1,此时FFl为1,其余触发器为0;控制单元在Sl状态时,则s1为1,当下一个时钟脉冲来到时,rRy和READ均为0,则控制单元保持在S1状态,这样要求FF1的输入为s1・TRy・READ,所以转换条件为「Ry・RDD。其余依此类推得出表10.2.3。表中没有列出s。为次态的情况,因为S。是直接由复位信号建立的,另外为方便起见,没有区别现态和次态的符号。由表10,2.3可以写出各触发器的输入逻辑关系式

FF0: DO=0 (reset异步置sO=1)

FFl: D1(s1)=s0+s1・rRy・ReAD+S3

FF2: D2(S2)=s1・rRy・READ・B・nf+s2・rRy・READ

FF3: D3(S3)=s1・rRy・READ・B・M

FF4: D4(s4)=S2・READ・TRy+s4

FF5: D5(S5)=s1・rRy+s1・rRy.READ・B+s2・READ+S5

=s1.rRy+s1・READ・B+s2・READ+S5

由图10.2.16所示的ASM图可以写出控制单元输出信号的逻辑表达式

CLR=S0 (低电平有效)

CⅣT=s3

0PEⅣ=S4

ERROR=S5

根据上述逻辑方程得出数字锁的控制单元电路如图10.2.18所示。图10.2.15所示为处理单元电路的结构图。如果D触发器选用74HC74。多路选择器选用74HC151,比较器选用74HC85,计数器选用74HC163,外加必要的门电路,将控制单元和处理单元组合起来就可以构成数字密码锁系统,数字锁系统电路图略。

比较两种控制单元的硬仵实现方法可知,触发器状态组合方法所用的触发器少,但组合电路相对复杂。一个触发器对应一个状态所用的触发器较多,但可以简化组合电路。对于寄存器数量多,而逻辑门相对缺乏的FPGA器件,采用后一种方法可以提高器件资源的利用率,提高电路的速度和可靠性。

上一篇:SDM857JG 数字系统的工作

公网安备44030402000607

公网安备44030402000607